Verilog中$fwrite总是在仿真成功后出错,请各位帮帮忙啊?

时间:10-02

整理:3721RD

点击:

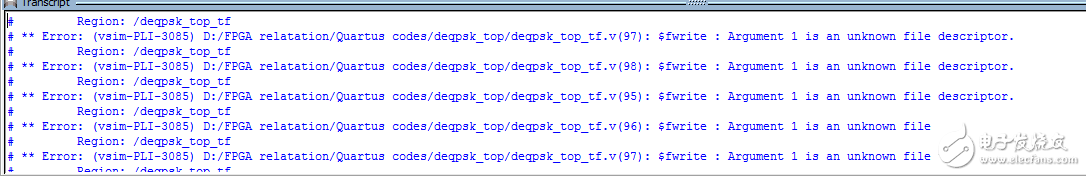

我是用QUARTUS调用Modelsim进行RTL级仿真,在Run all成功之后,才出现以上错误的。请大家帮忙看看到底是哪儿的问题

我在测试文件中用的$fwrite,这是我的测试程序:

- `timescale 1us/100ps

- module deqpsk_top_tf;

- reg rst;

- reg sys_clk;

- reg [11:0]din;

- //reg Hide_out;

- reg [11:0] v[0:250000];//读1000个应该就够了

- parameter [31:0]FCW_50K=858993400;//从250KHz分频得到50K分频控制字

- parameter [33:0]frequency=1717986918;//从250KHz分频得到100K分频控制字

- parameter newf_we=1'b1;

- wire signed[13:0]datai;

- wire signed[13:0]dataq;

- wire [27:0]df;

- //wire [33:0]frequency;

- //reg newf_we;

- wire [11:0]fsin_o;

- wire [11:0]fcos_o;

- wire signed[13:0]result1;

- wire signed[13:0]result2;

- wire signed[13:0]chouqu_out1;

- wire signed[13:0]chouqu_out2;

- wire signed[13:0]i_lpf;

- wire signed[13:0]q_lpf;

- integer vline;

- //integer i;

- deqpsk_top deqpsk_top(

- .rst(rst),

- .sys_clk(sys_clk),

- .din(din),

- .datai(datai),

- .dataq(dataq),

- .df(df),

- .frequency(frequency),

- .newf_we(newf_we),

- .fsin_o(fsin_o),

- .fcos_o(fcos_o),

- .result1(result1),

- .result2(result2),

- .chouqu_out1(chouqu_out1),

- .chouqu_out2(chouqu_out2),

- .FCW_50K(FCW_50K),

- .i_lpf(i_lpf),

- .q_lpf(q_lpf)

- );

-

- always #2 sys_clk

- initial

- begin

- $readmemb("D:/FPGA relatation/Quartus codes/QPSK_SYS_top/QPSK_OUT2.txt",v);

- end

- integer file1;

- integer file2;

- integer file3;

- integer file4;

-

- initial

- begin

- rst

- always @(posedge sys_clk)

- begin

- //$fdisplay(file,"%b\n",QPSK_OUT);

- $fwrite(file1,"%d\n",datai);

- $fwrite(file2,"%d\n",i_lpf);

- $fwrite(file3,"%d\n",chouqu_out1);

- $fwrite(file4,"%d\n",result1);

- end

- initial

- begin

- #1000000 $fclose(file1);

- $fclose(file2);

- $fclose(file3);

- $fclose(file4);

- end

- endmodule

呃,原来是$fclose后还继续跑,不再写了的话,在后面加个$stop应该也可以吧!

看不出,你试一下改一下fopen的文件路径,去掉空格行不行!

谢谢啦,已经解决啦,嘿嘿不应该把$fwrite写在always块里,如果这样每当时钟上升沿就会写入文件,而我在100000时刻就把文件关闭了,所以在运行100000时间后会出现错误,所以我把$fwrite写在initial模块里了,重复写100000次,这样就不会报错了,改后程序如下:

- `timescale 1us/100ps

- module QPSK_SYS_top_tf;

- reg sys_clk;//250KHz

- reg reset_n;//复位

- parameter [31:0]FCW_CA=1717986918;//DDS频率控制字,由250KHz得到100KHz载频

- parameter [31:0]FCW_10K=171798680;//从250KHz分频得到10K分频控制字

- parameter [31:0]FCW_50K=858993400;//从250KHz分频得到50K分频控制字

- wire Base_Signal;

- wire signed [1:0]Ik;

- wire signed [1:0]Qk;

- wire signed [1:0]Ik_nc10;

- wire signed [1:0]Qk_nc10;

- wire signed[11:0] Ik_bsf;

- wire signed[11:0] Qk_bsf;

- wire signed[11:0]Ik_f;

- wire signed[11:0]Qk_f;

- wire signed[11:0] I_OUT;//输出

- wire signed[11:0] Q_OUT;//输出

- wire signed[11:0] QPSK_OUT;

- wire signed[11:0]fsin_o;

- wire signed[11:0]fcos_o;

- wire signed[11:0]Ik_nc;

- wire signed[11:0]Qk_nc;

- QPSK_SYS_top QPSK_SYS_top(

- .sys_clk(sys_clk),//240MHz太大了 改为250KHz

- .reset_n(reset_n),//复位

- .FCW_CA(FCW_CA),//DDS频率控制字

- .FCW_10K(FCW_10K),//10K分频控制字

- .FCW_50K(FCW_50K),//50K分频控制字

- .QPSK_OUT(QPSK_OUT),

- .Q_OUT(Q_OUT),

- .I_OUT(I_OUT),

- .Ik_bsf(Ik_bsf),

- .Qk_bsf(Qk_bsf),

- .Ik(Ik),

- .Qk(Qk),

- .Ik_nc10(Ik_nc10),

- .Qk_nc10(Qk_nc10),

- .Ik_nc(Ik_nc),

- .Qk_nc(Qk_nc),

- .Ik_f(Ik_f),

- .Qk_f(Qk_f),

- .fsin_o(fsin_o),

- .fcos_o(fcos_o)

- );

-

- always #2 sys_clk<=~sys_clk;

-

- integer file1;

- integer file2;

- integer file3;

- integer file4;

- integer file5;

- integer file6;

- initial

- begin

- sys_clk<=0;

- reset_n<=0;

- file1=$fopen("D:/FPGA relatation/Quartus codes/QPSK_SYS_top/QPSK_OUT.txt","w");

- file2=$fopen("D:/FPGA relatation/Quartus codes/QPSK_SYS_top/QPSK_OUT2.txt","w");

- file3=$fopen("D:/FPGA relatation/Quartus codes/QPSK_SYS_top/fcos_o.txt","w");

- file4=$fopen("D:/FPGA relatation/Quartus codes/QPSK_SYS_top/Ik_bsf.txt","w");

- file5=$fopen("D:/FPGA relatation/Quartus codes/QPSK_SYS_top/Ik.txt","w");

- file6=$fopen("D:/FPGA relatation/Quartus codes/QPSK_SYS_top/Ik_f.txt","w");

- #2 reset_n<=1;

- end

- //always @(posedge sys_clk)

- //begin

- // //$fdisplay(file,"%b\n",QPSK_OUT);

- // $fwrite(file1,"%d\n",QPSK_OUT);

- // $fwrite(file2,"%b\n",QPSK_OUT);

- // $fwrite(file3,"%d\n",fcos_o);

- // $fwrite(file4,"%d\n",Ik_bsf);

- //end

- initial

- begin

- #2 repeat(100000)

- begin

- #4 $fwrite(file1,"%d\n",QPSK_OUT);

- $fwrite(file2,"%b\n",QPSK_OUT);

- $fwrite(file3,"%d\n",fcos_o);

- $fwrite(file4,"%b\n",Ik_bsf);

- $fwrite(file5,"%b\n",Ik);

- $fwrite(file6,"%d\n",Ik_f);

- end

- #100000 $fclose(file1);

- $fclose(file2);

- $fclose(file3);

- $fclose(file4);

- $fclose(file5);

- $fclose(file6);

- end

- endmodule

应该可以,不过我没试哈

小编的测试文件写的真好。