时钟经过PLL是否可以减少jitter?

时间:10-02

整理:3721RD

点击:

如果一个时钟经过一个时钟器件(buffer+PLL),这个器件的时钟输出相对时钟输入是否可以减小一些jitter ? 有实际项目,和芯片制作的哥们给些建议。 简单的说就是同一指标RMS值,输入是10ps,而经过PLL输入变成5ps了。

常见的CDR一般是PLL,但也有DLL,比如Xilinx

再举一个例子,采用81134,固有抖动大概是十几ps,但送给PLL后,表现只有几个ps

可以,但要好的PLL设计才行,因为PLL本身也会带来jitter,低质的PLL会适得其反。

是啊,理论是可以消除一些jitter的,就是担心适得其反。

可以的需要HW ENGNEER 设计电路

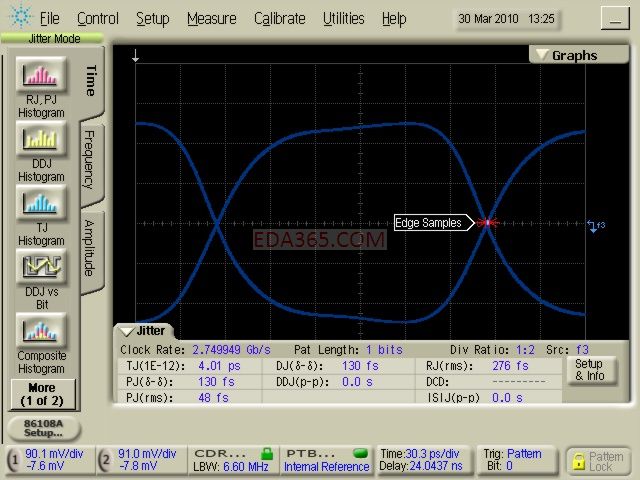

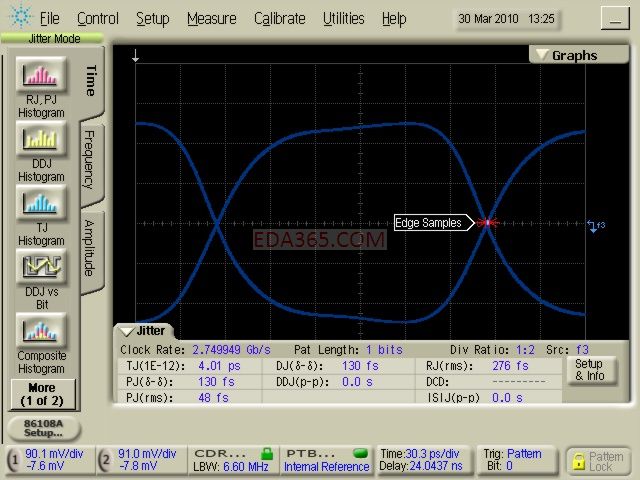

诚如Allen所言,PLL会将带宽以内的抖动跟踪掉,常见的PLL带宽为1~10MHz,但另一方面,PLL自身也存在固有抖动,会传递到下一级。

注意,PLL跟CDR还是有区别的。PLL如何将带内抖动跟踪掉?所谓跟踪,只有在CDR中,当Data与Clk做减法时才有。PLL是对输入时钟的带外抖动抑制掉。

明白,而抑制的实质是因为PLL内部存在的LPF,但另一个注意的地方是所谓的Knee点的抖动传递。

常见的CDR一般是PLL,但也有DLL,比如Xilinx

再举一个例子,采用81134,固有抖动大概是十几ps,但送给PLL后,表现只有几个ps

谢谢各位的关注,现在的实现方式基本都是APLL来实现Jitter的消除。08年的时候,由于芯片的要求比较高,而且商业芯片的性能确实也存在一些风险。

现在商业芯片DPLL+APLL集成的方式,这个问题基本已经能解决了。而且Jitter的测量,现在也越来越重视Phase noise的指标,直接跟内部的PLL的相关。

stupid ,多谢,我也在SH,不过去Lab的时候,很少能看到你,呵呵。

回复 liqiangln 的帖子

呵呵,随着抖动预算越来越紧张,链路中的每一部分都必须仔细考虑,而且必须持续不断的改进,才能满足貌似“变态”的要求。

在PLL的设计上,Altera和Xilinx现在都用模拟的。

而相噪的测试,类似于对VCO之类的,最好用的仪器是信号分析仪。