问一DDR3 时序预算的问题

时间:10-02

整理:3721RD

点击:

时序预算公式:

Tvb-Tsetup-Tboard_skew=Tsetup_margin

Tva-Thold-Tboard_skew=Thold_margin

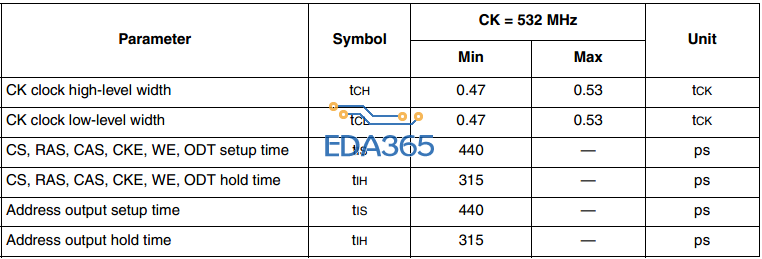

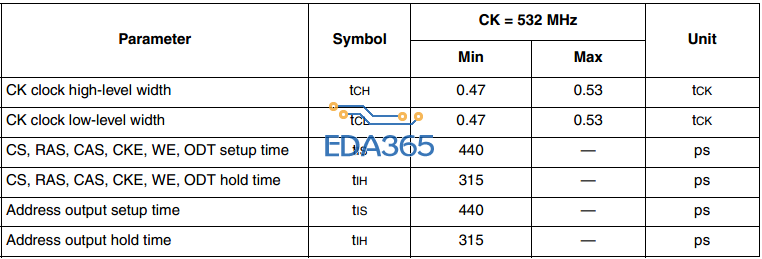

用下图提供数据得,Tsetup_board_budget=440-300=140ps

Thold_board_budget=315-300=15ps

问题:

15ps的板级预算,怎么可能满足?单算Vref的抖动就已经不能满足了。遇到这样的问题,各位大侠是怎么解决的?

Tvb-Tsetup-Tboard_skew=Tsetup_margin

Tva-Thold-Tboard_skew=Thold_margin

用下图提供数据得,Tsetup_board_budget=440-300=140ps

Thold_board_budget=315-300=15ps

问题:

15ps的板级预算,怎么可能满足?单算Vref的抖动就已经不能满足了。遇到这样的问题,各位大侠是怎么解决的?

高手还是很少啊

看到DATA还有140PS的MARGIN, 但ADD/CMD/CTRL很少。确实比较糟糕。

但DDR3 ADD/CMD/CTRL 有1T/2T的技术,2T简单来说就是CLK 2个周期采样一次add/cmd/ctrl,所以ADD的频率只有一半DATA频率。

上面的表格应该是1T的时候的TIMING. 到2T的话,应该margini还是很大的。

注意:有的DDR3 odt,cke,CS只能1T模式操作

http://www.eda365.com/forum.php? ... 80&highlight=1T

问下,一个DDR3 1333速率,在仿真时,它的clk频率和数据信号以及地址/控制信号的频率分别是多少呢?能否解答下,谢谢。

clk=667

data=1333

c&a=667

C&A=667我是按照3#的说的1T模式。

3#有句话说2T时ADD的频率只有一半DATA频率,个人感觉应该是四分之一频率。1333是上下沿都采样(因为是ddr),clk还是667,所以2T时候ca应该是667的一半,也就是1333的四分之一。不知道理解的对不对。