克服链路损耗

时间:10-02

整理:3721RD

点击:

2007-05-15

Martin Rowe,Test&Measurement World资深技术编辑

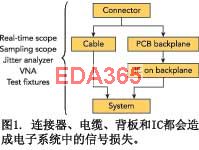

信号完整性测量是高速通信系统开发的基础。信号频率越高,就更易受干扰而劣化。数字信号(尤其是高于1Gbps的信号)在通过连接器、印刷电路板(PCB)走线、过孔、IC管脚和电缆时,会损失振幅并累积抖动(图1)。因此,传输通道会“伤害”到一个信号的完整性。

数字电路设计者经常依赖信号完整性(SI)实验室和工程师来描述传输系统的特性,通过创建HSPICE模型,设计者可以仿真单个电路或整体系统的性能。有了这些模型,设计者就可以预测一个元件在时域和频域中的表现。

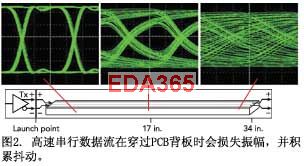

图2表示一个信号通过标准FR4 PCB板上一根走线时的劣化情况。一个带有清晰眼图的串行数据流,经过34in走线的传输后,信号已不能识别。设计者可以对造成眼图闭合的失真进行补偿,如为数据接收器增加自适应均衡器,但这样做需要知道眼图的情况。

注:上图中,整个链路长度40英寸,背板34英寸,2个子卡各3英寸,信号速率6.25Gbps.

连接器与电缆

连接器、电缆、背板和元件制造商一般是在时域中对自己的产品作测试和建模,如用采样示波器和实时示波器、误码测试仪(BERT),以及时域反射计(TDR)等。他们也会用微波测试设备作频域测量,如频谱分析仪和矢量网络分析仪(VNA)。

Tyco Electronics是一家制造串行数据流和微波信号连接器的厂商,它的电路测试与设计总监Dave Helster说:“我们在高达12Gbps的数据速率下测试连接器,频率可达20GHz。”该公司的工程师在时域中做TDR测量,以确定一款连接器的阻抗。在频域中,工程师用VNA为自己的连接器生成S参数模型。

在这种高频下,测试夹具、探头和电缆都会使信号受到损害而劣化。Tyco Electronics的工程师必须用标准来校准自己的测试设置,然后对测试设置的结果作数学补偿,以确保他们测量的是待测设备(DUT)的S参数。当工程师了解到一个测试设置在频域中影响信号的方式时,他们会在自己测量时使用一些校正因数,从中产生一个针对DUT某个特性的模型,如频率响应。

在电缆制造商W.L. Gore & Associates公司,SI工程师要确定微波电缆在110GHz频率下的特性。他们在电缆上用高达10Gbps的数字信号测量S参数。技术开发负责人TameraYost说:“我们测试的数据速率最低是5Gbps。”Gore的SI实验设备可以运行在12Gbps。

由于很多串行数据流采用差分信令,每根电缆需要测量四个端口的S参数。当使用双端口VNA做四端口测量时,实验室的SI工程师要设计一个使用微波开关的测试箱。

尽管电缆的高频衰减高于低频衰减,低频测量仍然很重要,因为串行数据接收机上的均衡器是根据不同的频率来处理信号。所以Gore的SI工程师要用两台VNA来获得一根电缆特性的完整图像。一个VNA覆盖30kHz至1GHz,另一台则覆盖1GHz到20GHz。

为了分析电缆和连接器在数字信号上增加的抖动,Yost及其同事使用一台有抖动分析软件的数字通信分析仪。Yost指出:“五、六年前,你只需要测量总抖动(Tj),然后将其分解为固定抖动(Dj)和随机抖动(Rj)。但现在不这么简单了。我们必须根据比特模式,测量与数据相关的抖动(DDj)。”DDj测量使工程师能了解到哪种通信协议会影响信号质量。

电路板与背板

Gore的SI工程师们还要研究PCB材料对高频信号的影响方式。他们知道电路板厚度对信号的影响。PCB越厚,就有更多的过孔变成类似‘树桩’样的传输线,因为它们会辐射干扰,并产生信号的反射,从而降低信号质量。

此处‘树桩’指 stub

Elma Bustronic的工程师们在设计背板时也遇到类似问题。工程总监Bagdan Gavril说:“由于‘树桩’问题,背板厚度现在要小于4mm。”过孔长度应只达到要求的长度,过孔中超长多余的金属会表现得像另一根走线。Gavril指出:“(多余金属所产生的)额外的电容可以毁掉一个信号。”

Gavril称在高于1GHz的频率下,必须特别注意电路板设计的错误,而在低频时则不重要。超过3GHz 时,每一点瑕疵都很关键。Elma 现在客户指定的数据速率为6.25Gbps,Gavril预计在2007年底前就会有对10Gbps的需求。

彼时,华为已在使用10Gbps背板。

Elma Bustronic的SI工程师用VNA确定背板中传输通道的特性。他们测量阻抗,进行眼图测量,还测量背板的抖动。他们还要测S参数,并为客户生成HSPICE模型,其中包含来自连接器和PCB模型的数据。因此,信号完整性是一个链条,包含从连接器到电路板、有源元件,直到系统。

有源元件

没有现场可编程门阵列(FPGA)这类IC就不成其为完整的电子系统,FPGA制造商Xilinx的SI工程师向连接器、电缆和背板公司一样要测量很多的参数。该公司的SI工程师负责确定SerDes发射机和接收机的特性,并为客户提供用于系统设计的 HSPICE 模型。

公司系统I/O与SerDes器件经理Jerry Chuang和同事亦在研究PCB设计和电路板材料对信号的影响。但Xilinx的客户是自己设计PCB,因此必须依照Xilinx产品的信息来确定自己传输通道的特性。

正如Xilinx指出的,Demo板的主要用途是Demo,不能照搬PCB叠层和电路板材料到自己的应用中,必须量体裁衣的制定叠层,挑选板材。一般来说Demo板的材料要比实际应用的材料高级,因为这样才不会让较差的材料影响芯片的Demo。另一方面,选择高性价比的板材,得先得到损耗预算,一般来说,发射端和接收端的均衡加起来不会超过10dB,这样无源通道的插损不能超过15dB。确定下来以后,就得做测试板实验,实验项目包括过孔,连接器,走线带来的损耗。

Xilinx工程师特别注重抖动问题。他们必须向客户证明自己器件的抖动性能,因为抖动是与协议有关的。SONET、PCI Express和XAUI这类协议在不同数据速率下会产生不同的Tj、Dj和Rj。

Chuang说:“我们同时用采样示波器和实时示波器测量串行总线发射器上的抖动。我们需要了解每家示波器制造商分解抖动的方式,因为存在着差异。”Xilinx SI实验室使用的是高端实时示波器,其带宽可以达到公司器件支持的数据速率。

看来抖动测试就像盲人摸象的问题,不光Altera注意到啦,Xilinx也注意到啦。小声的说,我们也注意到啦。

IC设计者会遇到一些无源元件制造商不会遇到的问题。IC需要电源,电源会影响信号的完整性。LSI Logic的首席设计工程师Mark Marlett说:“信号完整性开始于DC。”指出这一点是因为他公司的ASIC需要高达7A的电流,而电源在空载时不产生噪声。公司的SI工程师开始寻找电源噪声影响信号质量的方式。例如,电源的噪声可以增加时钟信号的抖动。

为了评估电源的影响,工程师们将查看某款器件在已通电但处于空闲状态,只有时钟运行时的情况。然后,他们激活部分ASIC,增加电源供给的电流,并观察增加的电源负载对抖动的影响。他们还会研究背板、电缆和连接器对信号完整性的影响方式。

是的,SSN会转化为时钟或数据中的抖动。

系统中的 SI

整体电子系统的制造商们要在用连接器、背板、电缆和IC组合构成系统时考虑有关SI的问题。有一家公司叫QLogic,是一个存储局域网络的制造商。QLogic的SI实验室有四名工程师,他们测量S参数、上升时间、抖动、符号间干扰、噪声等级以及光功率。他们还要测试接收机的抖动容限。对光纤系统而言,数据速率可达8.5Gbps。

QLogic首席工程师Douglas Zhao强调了抖动测量的重要性。“我们测量发射数据流中的 Tj、Rj、DDj和正弦抖动[sinej]。我们在纯净的数据流中增加抖动,以测试接收机的抖动容限。”SI工程师还使用一个纯净信号并减少信号的光功率来测试接收机。他们经常向客户公布测试结果。

话说,这位Douglas先生我见过,他对我们说,他现在比较关心PCB上的阻抗和损耗,也就是On board测试。

QLogic工程师还用实时示波器和频谱分析仪测量PCB电源层的噪声。频谱上的尖峰通常表示元件和PCB上的共振,这会损害信号完整性。

公共地

无论是对元件或整体系统,SI工程师都倾向于做相似类型的测量,因此也会遇到类似的障碍。也许他们面临的最大挑战就是寻找一种探查电路和信号的方式。

为简化这个工作,很多公司的工程师都开发了测试板和测试夹具。当然,SI工程师必须校准连接设置,以补偿测试板或夹具本身对信号完整性的影响。

例如,Elma Bustronic使用一个能通过SMA连接器同时接入到八个差分信号对的测试板。测试板可短路亦可开路,并有一个可直接插入背板连接器的MicroTCA边界连接器(图3)。

LSI Logic的Marlett使用图4所示的测试板。其测试设置能够测量进、出ASIC信号的抖动和眼图。

Gore的SI工程师设计了一个测试夹具,可以测试大量电缆。差分电缆的阻抗是100Ω,但测试设备的输入阻抗是50Ω。该夹具可以使 SI 工程师连接到大量电缆,而无需增加SMA连接器,因为SMA连接器也像信号路径中所有东西一样会损害信号。

有用的测量经验

如何开始成为一个SI工程师?尽管这个问题没有简单答案,但RF经验是必需的,因为数字信号也会呈现模拟特性。拥有RF工程师的企业的优势在于,他们可以向数字工程师讲授模拟方面的经验。具有统计学背景亦是一个有利条件。

在QLogic,SI工程师都有不同的专业领域。一个人有系统经验,另一个专门建模,第三个人则有测试设备规范和性能方面的专业能力。

对于Gore这样的大型企业,整个SI实验室可以包含不同的专家。该公司位于马里兰州 Elkton的实验室主要负责数字和微波测量,但它在德国的工程师则是EMI专家。

当有人问道SI工程师应具备什么技能时,Agilent公司测量开发工程师Greg LeCheminant回答说:“你需要有大量的测试经验。”

Tyco的Helster补充说:“做频域分析的经历也有帮助。但多数情况下,我们需要非常积极、有学习意愿的工程师,因为其它同事不会告诉你信号完整性问题。”

是的,这几点简直可以当作招聘SI工程师的标准。

更多信息

Rowe, Martin, “Jitter discrepancies: not explained,” a sidebar in “The scopes trial,” by Dan Strassberg, EDN, February 6, 2003. www.edn.com.

“Setting up a Signal Integrity Lab,” Wavecrest, Eden Prairie, MN. www.wavecrest.com.

所有的图都看不见······