零中频架构在无线电设计中的优势

就要选择高效的架构,该架构能针对目标工艺进行优化。类似于图中所示中频采样接收器的架构涉及到大量的高频和中频频率,难以在低成本工艺的基础上进行扩展,因此,要消耗大量功率以支持所需频率。然而,如图2所示的零中频架构能立即降低至直流(基带)的目标频率,因而可以实现频率最低的电路。

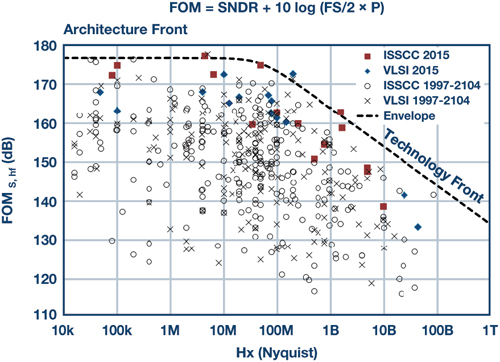

类似地,通过带宽来解决这个问题也是非常低效的。类似于直接射频采样的架构可提供较宽的带宽,并且具有极大的灵活性。然而,据Walden3 和Murmann.4在文中所述,增加系统带宽始终都会提高功耗。

除非需要原始带宽,否则,对多数接收器应用来说,仅仅通过带宽来解决这个问题并不是一种经济的解决方案。这些长期研究的数据表明,转换器的发展有两个方面值得关注。技术面取得了一些进步,能以动态范围和带宽的形式显著提高内核的交流性能。架构面在内核架构的整体效率方面有所进步。一般地,曲线先是向右移动,然后随着设计的优化,开始向上运动。对于通信应用,操作趋向沿技术面进行,其中,从线条斜率来看,转换器效率大约下降了10 dB/十倍频程,如图7所示。在此斜率下,使带宽增加一倍会导致功耗增加两倍。然而,在把这些内核集成到功能器件中之后,效率就有所改善,当其靠近架构面时,功率损失接近2。

图7、内核ADC技术的品质因数

对于关心功耗的应用来说,结论是,功耗最低的解决方案是带宽和采样速率均针对应用而优化过的解决方案。搭载Σ-Δ转换器的零中频采样设计就针对这类应用进行了优化。依据具体的应用,采用零中频接收器比中频采样架构可节省50%或以上的功耗,比直接射频采样可节省高达120%的功耗。

功耗还与成本直接相关。更高的功耗不但会提高封装成本和电源成本,而且对于电路消耗的每瓦特功率(设电费为12美分/千瓦时),每年每瓦特的运营成本会超过1美元。鉴于许多电子器件成本较低,其一年的运行成本就可能轻松超过其直接成本。因此,随着集成式无线电解决方案选项的推出,对成本和功耗敏感的应用必须选择谨慎地做出权衡。选择会不必要地增加功耗的架构,结果不但会增加功耗,还可能会影响解决方案的长期运行成本。

性能增强

无线电设计有若干重要的关键指标需要注意。其中包括噪声系数(NF)、线性度(IP3、IM3)、降敏、选择性等。在正常的无线电规格以外,还有一些规格也很重要,但用户往往看不到。其中包括规格分布和漂移与时间、电源、温度和流程的关系。零中频架构符合关于无线电设计的这些和其他关键要求。

通过温度、电源和流程跟踪

全集成式收发器架构的一个优势是,对于设计合理的无线电,器件匹配可能要好得多,不仅在起初是这样,而且如果设计合理,器件可以有效地进行流程、温度、电源和频率跟踪。运用通常嵌入这些集成解决方案中的信号处理技术,可以较好地消除任何残余的失配问题。虽然对IC设计来说,这是非常典型的情况,但是,无线电集成的不同之处在于,在零中频设计中,由于依赖于频率的所有项均部署于片上,所以,这些项也可以实现跟踪功能。如图1所示的典型无线电包括一个片外中频滤波器。该中频滤波器的特性会随时间、温度或器件而变化,与片上的任何元素均无关,并且不能对其进行跟踪。然而,集成滤波器的一个主要优势是,因为其以片上器件构建,所以,器件是可以扩展的,或者可以按比例相互跟踪,以保持性能稳定。对于那些不能通过设计稳定的项,可以轻松进行校准。最终结果是,在预计器件差异时,所需要的裕量要远远低于所有器件均无关的分立式设计。

例如,为混频器、中频滤波器、中频放大器和ADC各分配1 dB的噪声系数,这种做法并不罕见。在制定性能预算时,必须把这些差异级联起来。然而,在集成式设计中,所有关键技术规格要么相互跟踪,要么通过校准予以排除,结果可实现1 dB的单一器件差异,极大地简化了信号链差异。相比各项不相关的设计,这可能会对设计造成重要的影响;在各项不相关的设计中,需要额外的系统增益来抵销可能会增加的噪声—会影响到最终产品的成本、功耗和线性度。在如图2所示的集成式设计中,性能总差异要远远小于不相关设计,因此,只需较小的系统增益。

高级校正技术

在过去,零中频接收器通常有两个领域会引起人们的担忧。由于复合数据是用一对表示实部和虚部的实数级联网络生成和表示的,结果就产生了可能表示各信号链增益、相位和失调的误差,如图8所示。

图8、表示增益、相位和失调项的正交误差

这些误差在频谱中表现为镜像,也是妨碍这些架构广泛普及的主要原因。然而,作为一种集成式解决方案,通过模

无线电 相关文章:

- 用于移动宽带基础设施的新一代无线电数字前端解决方案(11-11)

- 现代无线电接收机的系统噪声系数分析二:Y因子噪声因子测量法(07-03)

- 现代无线电接收机的系统噪声系数分析一:级联接收机的计算(07-01)