物联网方兴未艾,飞思卡尔运筹帷幄细化QorIQ通信处理器

从模拟制式手机到2G、3G、4G甚至是未来的5G,每到转折期就有一些人被技术牵绊而不知何去何从,飞思卡尔半导体总是能应景推出相应的通信处理器等创新产品,为通信时代的跨越保驾护航。在物联网时代,通信处理器不再属于稀缺资源而被少数企业掌握,并且更新速度加快,倒逼知名厂商处于"逆水行舟不进则退"的境地,要继续做领头羊,需要针对新时期的"痛点"更新产品。飞思卡尔QorIQ T1024/14和T1023/13通信处理器就是众多新品之一,这些新处理器采用28 nm技术,将性能领先的Power Architecture e5500处理器内核与运行频率高达1.4 GHz的先进缓存架构、应用领先的卸载引擎和面向未来、低功耗的内存子系统整合在一起,它们主要针对低成本的企业和服务供应商边缘和网络控制应用。

"芯"核心的执着

双核QorIQ T1024和T1023通信处理器及单核QorIQ T1014和T1013通信处理器配备64位内核,基于Power Architecture技术构建,提供网络和电信应用所需的高性能数据通路加速架构(DPAA)和网络外设总线接口。ARM核现在从低端到高端已经全面铺开,很多处理器厂商都在逐渐弱化甚至放弃自有架构处理器的开发。飞思卡尔采取了"双管齐下"的策略,虽然其基于ARM核的处理器已经跑在同行前列,但却在仍然执着地坚持自己"芯"核心——Power Architecture。QorIQ T1024/14和T1023/13就基于单/双Power Architecture e5500内核,运行频率达1.4 GHz。采用混合32位模式,支持原有软件,并可向64位架构平稳过渡。

e5500架构是飞思卡尔e500内核的两倍,它的设计频率高达2.5 GHz,可以运行在64位或32位模式。64位e5500内核实现了诸多改进,包括支持多核SoC实施方案以及异构多核处理器。在e5500 64位内核上的技术进步,实现了集成度和性能的独特结合,在非常低的功率范围内达到了非常高的性能水平,为嵌入式能效设定了一个基准。e5500技术基于Power架构指令集(ISA)v2.06,有以下特性:一个乱序执行的7级流水线;64 GB的更高平面寻址内存空间;6高性能经典浮点单元(FPU)支持IEEE754浮点运算;混合32位模式,支持传统的软件,并可过渡到64位架构;L1缓存,背面L2缓存加上共享L3缓存。

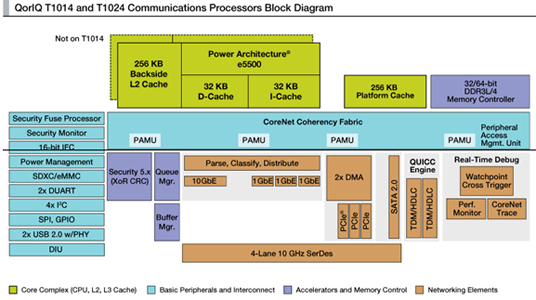

图1 QorIQ T1024/14通信处理器内部架构图

极速奔驰,接口不再是鸡肋

随着大数据时代对速率的要求激增,传统并行接口的速度已经成为瓶颈,取而代之的是速度更快的串行接口,于是原本用于光纤通信的SerDes技术成为了为高速串行接口的主流。它是一种主流的时分多路复用(TDM)、点对点(P2P)的串行通信技术。T1024/14和T1023/13就支持SerDes:4条高达10 Gb/s的通道,并支持SGMII、QSGMII、PCIe和SATA。其他网络单元也很有看点,如1×10GbE、3×1GbE或4×1Gb Gigabit以太网接口。

加速器和存储器控制也是保证速度的一个重要方面。数据路径加速架构(DPAA)包含加速特性,适用以下功能:数据包解析、分类和分发,支持调度、数据包排序和阻塞管理的队列管理,支持硬件缓冲管理,可缓冲分配和取消分配,集成安全加速(SEC)。此外,高达4.1 Gb/s的以太网MAC可作为DPAA的一部分。T1024/14和T1023/13还具有32/64位DDR3L/4 SDRAM存储控制器,带有ECC支持,高达1 600 MT/s。

新处理器的外设接口主要有:一个串行ATA (SATA 2.0)控制器,两个高速USB 2.0控制器,带有集成PHY,增强型安全数字主设备控制器(SD/MMC/eMMC),增强型串行外设接口(eSPI),两个I²C控制器,4个UART,支持NAND与NOR闪存的集成闪存控制器。

可扩展、可编程的基于RISC的通信协议加速引擎QUICC Engine技术主要设计用于下一代有线和无线接入应用,因此其也被集成到了T1024/14和T1023/13中。QUICC Engine支持原有协议TDM、HDLC、UART和ISDN,可以提供数据包流量、互通功能(无CPU干预)、多协议支持、很高的信道密度和软件兼容性,为融合分组网络开发先进而经济的解决方案。

作为通信处理器,为了不让数据在芯片内部"塞车",有效的互连是不可缺少的,新处理器具有CoreNet平台缓存,256 KB共享平台缓存;分层互连结构,CoreNet结构支持相干和非相干事务,CoreNet结构就像一个小管家一样,在CoreNet端点之间进行优先级排序和带宽分配。

防微杜渐,安全不再渐行渐远

千里之堤,溃于蚁穴,很多时候,危害往往来自细微环节。大数据、云的迅速发展似乎让安全性渐行渐远,在美国明星隐私照被曝光后,数据安全再次被推倒风口浪尖。通信处理器作为数据的一个重要关卡必须要重视安全性,防微杜渐。QorIQ T1024/14和T1023/13所有端口均带有MACsec,它是一个用以保护局

- RF功率器件的设计及应用(06-01)

- 飞思卡尔ZSTAR3无线传感器参考设计(07-04)

- 飞思卡尔QorIQ Qonverge系列多基站一体化设计方案(05-27)

- 网络“诱惑”为飞思卡尔LS1系列通信处理器带来机遇(10-12)

- 飞思卡尔小基站解决方案治理4G时代的无线网络“城市病”(08-18)

- 智能汽车演进从飞思卡尔车窗升降参考设计开始(04-12)