飞思卡尔小基站解决方案治理4G时代的无线网络“城市病”

应对无线网络"城市病"

随着城市人口越来越多、楼房越来越密集,无线网络也遭受着"城市病"的困扰,无线网络速率在人口密集地区一直不如人意。加上4G的迅速普及以及智能手环等各种可穿戴产品不断上市,就对无线网络提出了更高的要求,也直接给基站带来压力。

作为基站的"大脑",通信处理器一直备受关注,也是"兵家必争之地"。对于其发展趋势,普遍的观点是:高性能异构SoC将进一步发展,每个厂商将基于现有架构,配置性能更高的核,并且会采用多核DSP+多核CPU或者多核DSP+多核ARM。此外,还会集成更多的模拟部分,当然低功耗也是必不可少的,这种趋势也正是为了适应无线基础设施的发展需求。基站经历从模拟到数字、从窄带到宽带的发展历程,每4~5年就更新一代,但其发展方向一直没有改变,都是向高性能、高可靠、布网灵活、升级维护方便、节省全生命周期成本的方向发展。目前为了解决覆盖和容量问题,小基站如雨后春笋一般的迅速发展,因为数据传输速率越大,无线覆盖就越受到挑战,小基站也就更合适。需要指出的是,小基站不是只指四代,而是针对大规模的4G、3G以及GSM的支持上,它更多是用于热点的覆盖,包括大的社区、商场、办公楼以及校园网的覆盖。

为小基站而生的4核异构SoC

飞思卡尔三年前推出业界首款面向各种基站的多模无线基站处理器系列,便引领片上基站市场。飞思卡尔城域小区解决方案面向高带宽、低功耗的基带应用,并针对LTE (FDD和TDD)及WCDMA (HSPA+)城域基站应用进行了优化。今年2月推出的QorIQ Qonverge B3421 SoC面向快速增长的城市板块,巩固了飞思卡尔在无线网络领域的领导地位。

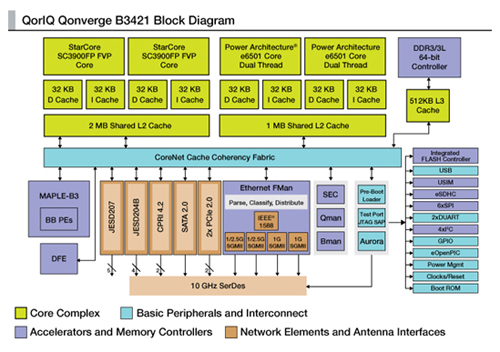

QorIQ Qonverge B3421无线基础架构片上系统基于先进的SoC架构,采用28 nm工艺技术制造,集成有数字前端(DFE),是一款高性能基带解决方案,适用于对功耗、尺寸和成本要求较为严格的小型小区部署。该器件就是采用双核DSP+双核CPU的异构形式,配备两个基于Power Architecture®技术的双线程64位e6501内核(带有AltiVec SIMD引擎)、两个基于StarCore技术的SC3900FP定点/浮点DSP内核,以及针对特定应用的加速器,具有卓越的处理性能,可在上行链路和下行链路都保持高数据吞吐量的同时,实现功耗最优化。B3421已为在LTE和Wi-Fi下运行进行了全面优化,适合采用FDD-LTE、TDD-LTE和LTE-Advanced协议的企业微微小区、户外微微小区和城域小区等小型小区基站。B3421内部架构如图1所示。

图1 QorIQ Qonverge B3421内部架构

从图1可以看到,贯穿在各核心部件中的是CoreNet,它是内部无阻塞缓存一致性交换结构,可以保持SoC中CPU、DSP、DDR3、MAPLE-B3等各核心部件数据交换畅通无阻,其每簇原始带宽高达42.5 GB/s。很多工程师常常抱怨多核处理器特别是异构多核SoC给他们的编程带来很多不便,难度太大。CoreNet配上可加快产品上市并优化性能的商业级VortiQa 第1层基带软件以及经过现场验证的层1/物理层(PHY),降低了异构多核带来的软件开发难度。

B3421的嵌入式CPU内核、DSP内核、基带加速器和DFE技术形成了一个片上系统解决方案,可处理从前端到回程的基站处理任务。借助集成式DFE功能以及符合行业标准的天线接口,可实现RFIC的无缝对接以及RF阵列的优化。外加可满足低功耗需求的以太网供电(PoE),可支持各种天线方案的JESD204B、JESD207和CPRI接口,用于连接Wi-Fi芯片组的PCI Express,用于本地内容缓存的SATA以及以太网SGMII回程接口,QorIQ Qonverge B3421成为业内集成度最高的城域小区基站SoC。

多重加速

作为基站处理器,即使是用于小基站,对于速度的追求也是不能含糊的。B3421采用多重加速技术让其可以"极速奔驰"。

(1)面向基带的多加速器平台引擎(MAPLE-B)支持LTE和LTE-Advanced (符合3GPP Release 11),包含针对以下功能的加速:支持解速率匹配和HARQ合并的Turbo解码器,支持速率匹配的Turbo编码器,Viterbi解码器,FFT/DFT,基于MMSE的MiMO均衡器,支持IRC、SIC、PIC和矩阵求逆加速;LTE PDSCH和PUSCH数据通路嵌入式处理链。

(2)采用线性化的数字前端(DFE)技术,能对波峰削减(CFR)、数字预失真(DPD)和数字上/下变频进行加速。该技术可改进功率放大器(PA)效率,并显著降低基站的功耗和成本,可帮助运营商增加容量并在用户密集地区增加覆盖。

(3)配备通路加速架构(DPAA):帮助数据包解析、分类和分发;支持调度、数据包排序和阻塞管理的队列管理;支持硬件缓冲管理,可缓冲分配和取消分配。

(4)面向加密/解密的安全引擎,包含针对以下功能的加速:IPsec、DLTS/CAPWAP、SNOW

- RF功率器件的设计及应用(06-01)

- 飞思卡尔ZSTAR3无线传感器参考设计(07-04)

- 飞思卡尔QorIQ Qonverge系列多基站一体化设计方案(05-27)

- 网络“诱惑”为飞思卡尔LS1系列通信处理器带来机遇(10-12)

- 智能汽车演进从飞思卡尔车窗升降参考设计开始(04-12)

- 物联网方兴未艾,飞思卡尔运筹帷幄细化QorIQ通信处理器(12-14)