一种0.1-1.2GHz的CMOS射频收发开关芯片设计

通状态,可以将M4耦 合过来的信号导通到地,由此便提高了开关的隔离度。当VDD为-1.8V,VSS为1.8V时,开关处于发射模式,与接收模式的原理基本相同。电阻R1、 R5、R7和R12与NMOS管深N阱相连接,用于给深N阱加偏压;栅极电阻R3、R6、R9和R11用来提高隔离度;R2、R4、R8和R10接晶体管 体端,用于体端悬福并且,为了进一步提高隔离度,所有体悬浮电阻的阻值都应足够大。

本宽带射频收发开关电路中,晶体管M1、M3尺寸为96μm/0.18μm,M2、M4尺寸为200μm/0.18μm,电阻R1~R12均为9K ohm。该电路采用Cadence SpectreRF 对开关电路进行电路设计、仿真优化。

2、测试结果

本开关电路设计采用GLOBALFOUNDRIES 0.18μm CMOS工艺。开关电路核心面积为0.015mm2,包括芯片测试焊盘的整体面积为0.53mm2,图4为该射频收发开关芯片显微照片。本次芯片片上测试 环境基于Cascade Summit 探针平台,如图5所示,采用Rohde & Schwarz的矢量网络分析仪ZVA40,使用TOSM(through-open-short-match)方法进行仪器校准。测试过程中,深N阱偏 置电压VCC始终为1.8V, 控制电压VDD和VSS为1.8V或-1.8V。输入、输出采用GSG射频探针进行片上测试。

图4 射频收发开关芯片照片(接收状态)

图5 射频收发开关测试平台照片

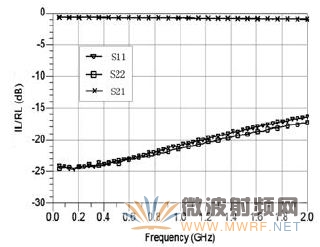

图6 接收模式下插入/回波损耗测试结果

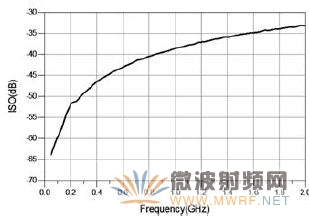

图7 接收模式下隔离度测试结果

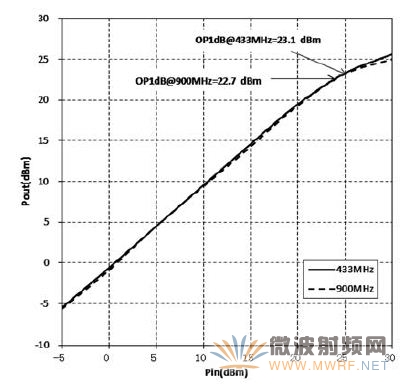

图6和图7均为该射频开关在接收状态下S参数测试结果。从图6中可以看出,在0.1-1.2GHz频段范围内,开关的插入损耗(S21)为-0.7dB左 右,且平坦度良好,输入、输出回波损耗(S11和S22)小于-20dB;从图7中可以看出,在整个频段内射频开关的隔离度(S13)均大于37dB,具 有良好的隔离特性。由于采用全对称结构,该射频开关在发射状态下的S参数测试结果与接收状态下相比基本相同。图8所示的为该收发开关在433MHz及 900MHz频率下的输出功率曲线及1dB压缩点。测试结果表明,两个频率的输出功率曲线1dB压缩点分别为23.1dBm和22.7dBm,且功率压缩 特性基本一致。

图8 输出1dB压缩点测试结果

结束语

本文设计了一种性能良好的超宽带全集成CMOS 射频收发开关芯片,芯片总面积为0.53mm2。测试结果表明,在1.8V电压供电条件下,该射频开关在0.1-1.2GHz频段内收发两路均可达到 0.7dB左右的插入损耗,小于-20dB的回波损耗以及优于37dB的隔离度。并且,在433MHz和900MHz频率下可分别实现23.1dBm和 22.7dBm的线性度。该电路满足0.1-1.2GHz频段无线宽带射频收发芯片的基本设计需求,并适用于RFID和GSM-R系统中的典型应用。

- 全集成CMOS GSM射频收发器的实现(02-07)

- CMOS RF模型设计指南(11-13)

- 3G中的CMOS基RF集成(02-22)

- CMOS技术缓解了RF电路在SoC中的集成挑战(04-11)

- 低功率CMOS无线射频芯片设计要点(04-18)

- CMOS PA陷入成本和性能两难,“单芯片手机”梦受阻(06-27)