CMOS PA陷入成本和性能两难,“单芯片手机”梦受阻

但和初创公司的高调相比,RFMD、Anadigics和英飞凌等现有供应商仍对CMOS PA持怀疑态度,认为CMOS PA很难在成本和性能上取得平衡,即使是收购了AXIOM的Skyworks也认为CMOS PA在3G和4G等高端应用市场空间有限。而SiGe半导体等公司则在走中间路线,认为取代砷化镓功放的将是SiGe BiCOMS工艺,而不是CMOS工艺。

成本和性能难以平衡,CMOS PA限于2G市场

众所周知,因为符合摩尔定律,CMOS工艺的优势是低成本、低功耗和高集成度等,从某种意义上来说,半导体技术发展的历史就是CMOS工艺进步的历史。Javelin公司的CEO Brad Fluke表示:“历史证明,一旦可以基本满足某项应用所需的性能,那么在和其它工艺的竞争中,CMOS工艺总是胜利者。”

问题是,目前CMOS PA仍然难以在成本和性能间取得平衡,CMOS PA既达不到砷化镓功放的性能,成本优势也并非绝对。

一方面,虽然CMOS晶圆比砷化镓晶圆便宜很多,但CMOS功放的面积比砷化镓功放大,最终单个器件的成本优势并不像想象的那么明显。目前6英寸GaAs晶圆可以产出大约为5,000~10,000片功放,而8英寸硅晶圆可以产出的功放数量要比这个数目少的多。这是由于CMOS器件本身的特性决定的。RFMD公司的专家表示:“在CMOS 器件中,电流是沿着晶片表面横向流动的水平电流,而砷化镓HBT工艺器件,电流流动是纵向流动的垂直电流。所以砷化镓功放可以做到比CMOS功放小50%到70%。”

另一方面,从功放应用看,相对于CMOS器件,砷化镓器件有物理材料上的优势。虽然CMOS器件这方面的缺陷可以用更复杂的设计来弥补,但是这样一来,会大幅提高成本。比如绝缘硅(SOI)技术在射频领域中的应用。相比体硅基板上的CMOS晶体管,SOI技术提升了电子迁移率,有助于缓解大功率、高效率CMOS 功放制造中的一些问题。但CMOS SOI晶圆的成本远远高于常见模拟/混合信号CMOS工艺技术的成本。因此在3G/4G应用中,CMOS的成本优势会更小,因为更高性能要求采用更复杂、昂贵的架构设计。

对此,深圳广迪克科技有限公司总经理徐杰表示:“如果采用同样的工艺节点,CMOS PA能应用的频率比砷化镓PA要低得多。”作为新兴的射频PA供应商,广迪克的砷化镓PA已经开始大量出货,据称在效率、最高功率等方面都达到了国际同类产品的水平。为了把握PA的技术发展趋势,2009年末徐杰专程前往美国考察CMOS PA技术发展情况,得出的结论是近期CMOS PA不会成为主流,因此更坚定了开发砷化镓PA的决心。

因此,在2G手机等低端应用中,由于对线性度、频率、击穿电压、峰值电流、效率的要求相对较低,不需要CMOS PA采用太过复杂、昂贵的设计,因为成本优势,未来CMOS PA的市场份额可能持续扩大,但在3G/4G等高端应用中,受限于性能和复杂设计的成本提升,CMOS PA近期不会大规模取代砷化镓功放。

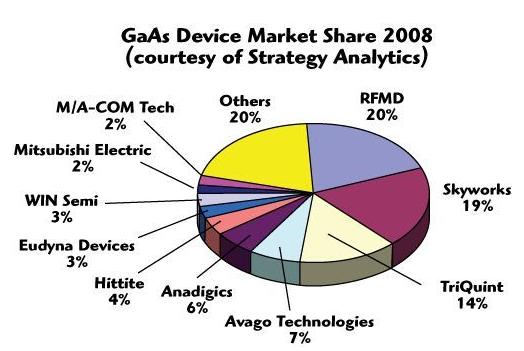

图:2008年全球砷化镓PA供应商排名

这从Skyworks已经售出总量超过 2,500 万颗的GPRS应用 CMOS功放中就可见一斑。Skyworks的市场总监Thomas表示:“在对性能不十分苛求的市场领域,CMOS PA的合理成本已经使其在 GPRS 应用上极具竞争力,成为 GaAs功放的替代产品,我们相信,这种趋势还将持续下去。”

但Thomas也坦承,在3G/4G应用上,砷化镓依然具有显著的性能优势,CMOS的成本优势也不再明显,因此在这些无线技术领域,CMOS PA的市场占有率不会有大幅提升。

例如在WCDMA应用中,大电流持续时间较长,电流达到400-500mA,而目前2G应用中的CMOS功放,电流超过300mA就无法承受。当然可以通过更复杂的架构设计提高CMOS功放的性能,但复杂的设计意味着更高的价格。

- 全集成CMOS GSM射频收发器的实现(02-07)

- CMOS RF模型设计指南(11-13)

- 3G中的CMOS基RF集成(02-22)

- CMOS技术缓解了RF电路在SoC中的集成挑战(04-11)

- 低功率CMOS无线射频芯片设计要点(04-18)

- 采用标准CMOS工艺设计RF集成电路的策略(03-15)