基于FPGA的LCD大屏幕拼接系统的设计

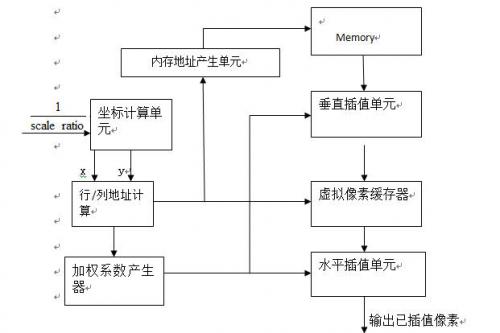

单元,如图4所示:

图3 插值放大模块的框图

3.2.1坐标计算单元

延展式线性插值要求源图像插值点周围有16个像素点,然后根据并行计算单元获得的插值点的坐标。由插值点的坐标可以决定临近的16个行和列点的坐标,接着就可以从memory中获得16个点的像素并执行线性插值。

线性插值的原理可分解为垂直与水平插值,例如在图4中,在水平方向上的像素点,是第一个虚拟像素的地址,能使从虚拟像素缓存器正确读取虚拟像素点与进行水平方向的插值。这样的操作不需要电路都同时在执行,因此只需要一行或列的地址计算电路。

图3 水平方向与垂直方向的插值

对于列或行地址计算器,输入信号决定水平与垂直方向的坐标。坐标数据包含10位的实数以及10位的小数部分。坐标数据的第9位是小数部分最重要的一位,它决定着小数部分是否大于0.5。同时由第9位控制的多路选择器控制用于输出正确的内存地址。如果输入的是列信号,那么行地址 ,

, ,

, ,

, 和垂直间隔

和垂直间隔 可由公式(1)到(3)得到,同理,列地址

可由公式(1)到(3)得到,同理,列地址 ,

, ,

, ,

, 和水平间隔

和水平间隔 能由公式(1),(2)和(4)得到。

能由公式(1),(2)和(4)得到。

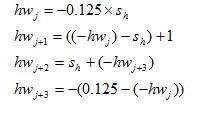

(1)

(1) (2)

(2)

(3)

(3)

(4)

(4)

3.2.2 加权系数产生单元

在设计的框图中,水平加权系数与垂直加权系数的计算并不是同时生产尽管它们都由公式(5)和(6)决定。因此,加权系数产生器产生水平及垂直加权系数,当控制信号为水平信号时,最终的输出为 ,

, ,

, ,

, ,相反的,则输出

,相反的,则输出 ,

, ,

, ,

, 。在延展式线性插值最大的计算量是加权系数的计算,而最复杂的运算却由最简单的两个加法器和两个减法器构成。

。在延展式线性插值最大的计算量是加权系数的计算,而最复杂的运算却由最简单的两个加法器和两个减法器构成。

(5)

(5)

(6)

(6)

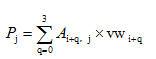

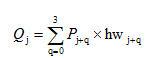

3.2.3 水平与垂直插值单元

根据公式(7)和(8),水平与垂直插值有同样的运算,但是它们是并行执行以提高整体的速度。水平与垂直插值的逻辑结构由图5所示,乘法器与加法器可以有效的完成输入的数据的卷积与拼配相应的4个加权系数来产生插值的电路。

(7)

(7)

(8)

(8)

水平插值单元 垂直插值单元

图5水平与垂直插值单元逻辑框图

3.2.4虚拟像素缓存器

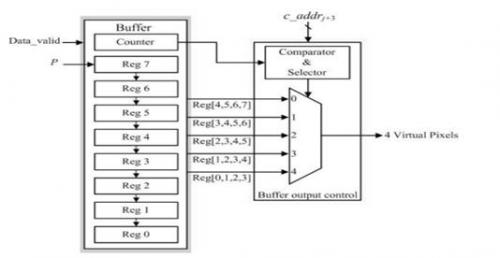

虚拟像素点是由垂直插值产生并存于虚拟像素缓存器中,在水平插值的过程被调用。一般来说,缩放比例会决定这缓存器输入与输出数据的速率,当放大的时候,每个虚拟像素会被重新用于水平插值以致于垂直插入器数据速率会比水平的要低,相反的,在缩小的时候,虚拟像素由垂直插值过程产生的会比水平插值过程所需求的要多。为了调节不同的数据速率,设计虚拟像素缓存器如图6所示,其中包含1个计数器,8个寄存器和缓存输出控制电路。在插值放大的过程中,缓存器有时会延缓垂直插值,虚拟像素数量比水平插值所需求的确定数量要多的时候,就会停止虚拟像素的产生。计数器则是记录着最新产生的虚拟像素点的列地址并存于reg7.比较器和选择器对比计数器和 的值来决定缓存器的输出。

的值来决定缓存器的输出。

图6 虚拟像素缓存器

4、验证

算法的验证是基于Xilinx Virtex-4 FPGA开发平台,对视频分割模块及延展式线性插值模块分别进行仿真,验证算法的正确性,再经反复的优化及测试,最后下载到开发板,验证输出的视频显示效果是否能够满足视频放大的应用需求,完成LCD大屏幕拼接系统的设计。

FPGA LCD 屏幕拼接 DVI解码 虚拟像素缓存器 相关文章:

- 德州仪器推出具备n因数与串联电阻校正功能的+/-1℃远程与本地温度传感器(09-15)

- 基于FPGA的超声波液体密度传感器(07-05)

- 基于FPGA的司机眼球跟踪疲劳检测报警系统(07-05)

- 智能手机传感器管理,FPGA比AP+MCU方案功耗低10倍(10-11)

- 采用MEMS麦克风实现复杂环境下对特定语音的提取与放大(06-02)

- 多款陀螺仪表头设计、平台测试、系统研究方案及应用实例(06-28)