基于FPGA的LCD大屏幕拼接系统的设计

素流 (包含视频像素数据和视频同步控制数据), 并控制4个子视频显示的相互时序关系; 各个拼接屏幕的像素点的扫描规律相同, 均为逐行扫描形式, 并且子视频像素点显示同步, 即行同步和场同步。

(3)视频插值模块实现对视频分割所得的子视频进行2×2倍地插值放大处理, 该模块采用并行处理方式, 四路子视频分别经过各自独立的视频处理通道;插值放大算法是基于在FPGA进行延展式线性(extended linear interpolation)待插值像素点的数据计算, 配合视频生成模块(VGASyncGen)产生的参考视频流, 并通过共享的行缓冲存储器实现插值像素数据的分时读写切换来实现的。所得到视频像素流包含完整视频像素流格式,并且符合较高分辨率的视频显示要求。

(4)视频输出模块,完成放大处理后的各个视频像素流输出到DVI 编码输出电路。保证各个显示屏幕得到的视频信号符合VESA 规定的标准时序要求。

3、算法的FPGA实现

3.1视频分割算法的实现

算法对数字视频的处理采用并行处理方式, 首先要对输入视频像素流进行分割处理, 得到四路具有完整视频格式的子视频, 并且输出的四路子视频具有相同的扫描规律, 即行同步和场同步;四路子视频中, 当有一个视频进行场变换或行变换时, 其它三路视频也要同时完成对各自视频的场变换或行变换;当显示屏在对屏上的第一行像素点进行扫描时,其余各显示屏也都在对各自屏上的第一行像素点进行扫描。尽管扫描规律一致, 但每个子屏幕所显示的视频图像内容却是不同的。

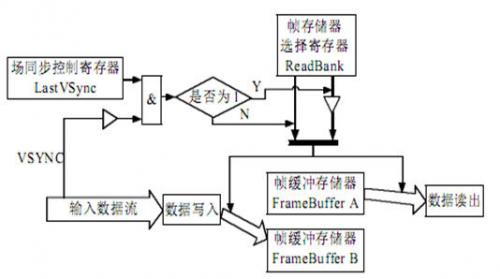

(1)片外SRAM分时切换: 所设计视频分割算法通过在外部SRAM 中对输入视频像素数据帧进行缓存,因为要进行不同顺序的读、写操作。为了保证对数据进行读写处理的连续性, 即对RAM的写入和读出不发生时间上中断, 因此须使用两组SRAM进行读、 写分时切换操作, 如图2 所示。

图2 SRAM读写切换示意图

在处理算法中使用了A、 B两组像素数据存储区, 用以记录单帧的视频像素数据。FPGA 的分时切换逻辑是依据输入视频流的场同步控制信号VSync发生由高电平到低电平的转换, 以此作为新数据帧到来的标识。场同步控制寄存器Last-VSync 存储的是像素流中前一个像素点的场同步控制信息,如果 LastVSync 为高电平"1"且当前像素点的场同步信号VSync 为低电平 "0" , 则表示新的像素帧开始。那么帧存储器选择寄存器ReadBank则取反, 从而提示数据写入和读出控制逻辑进行读/写帧缓存的切换;相反,如果场同步控制寄存器LastVSync 与当前像素点的 VSync 值同时为有效"1" ,即表示没有新的像素帧的到来, 帧存储器选择寄存器不发生变化。 这样将输入数据轮流分配到这两组帧缓冲存储器。即可实现对输入视频像素流的无缝缓冲与处理。

(2)子视频同步控制获取: 输入视频图像在一帧内的行同步控制信号(HSync)和场同步控制信号(VSync)与输出的四路子视频的行同步控制信号及场同步控制信号并不一致,因此需要在算法中加入一个参考视频像素流,用于提供子视频行场同步控制信息; 该参考视频流不包含像素点的R、 G、 B数据信息, 但满足输出子视频流所需要的行、 场同步控制信号的时序特征。在形成的单帧视频图像中其水平方向和垂直方向像素点个数为输入视频像素点个数的一半,视频刷新频率与输入视频保持一致。

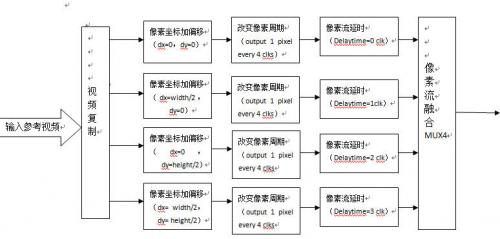

视频流的控制逻辑如图 3 所示, 过程如下:第1 级,将参考视频流复制成4个子视频流(Split4), 第2级是对每一个视频像素流地像素坐标增加偏移量(dx, dy), 使其对应不同的子视频像素点的显示位置,例如,对第2 个子视频, 由于它要读取输入视频的右上方位置的视频图像数据,设置其横向偏移量为Width/2 和纵向偏移量为0,其它的子视频与之类似。复制出的四路参考视频要转换成串行像素流,输入到帧缓存读取像素数据,第3级操作就需要改变它们的像素周期,使子视频在每4 个像素周期内输出一个有效的像素数据, Cycles为预设置的控制像素周期(Cycles设置为 4), 使有效像素数据的时钟频率与子视频像素频率相同。最后,对四路参考视频像素流作不同的延时处理, 再经过像素流融合(MUX4)为串行的视频像素流。这样把并行像素流转为串行像素流,串行像素流读取一帧像素的时间与输入视频像素流写入一帧像素的时间是相等的。像素流融合操作对输入的四路视频, 通过设置控制参数(control), 在不同时钟下选取带有偏移量的视频像素点。

图 3 视频流的控制逻辑图

3.2视频插值放大算法的FPGA实现

视频插值放大模块包含了坐标计算单元、加权系数产生器、垂直插值单元、虚拟像素缓存器与水平插值

FPGA LCD 屏幕拼接 DVI解码 虚拟像素缓存器 相关文章:

- 德州仪器推出具备n因数与串联电阻校正功能的+/-1℃远程与本地温度传感器(09-15)

- 基于FPGA的超声波液体密度传感器(07-05)

- 基于FPGA的司机眼球跟踪疲劳检测报警系统(07-05)

- 智能手机传感器管理,FPGA比AP+MCU方案功耗低10倍(10-11)

- 采用MEMS麦克风实现复杂环境下对特定语音的提取与放大(06-02)

- 多款陀螺仪表头设计、平台测试、系统研究方案及应用实例(06-28)