全局快门像素技术和CMOS图像传感器形成强大的技术组合

传统上,全局快门像素技术主要用于CCD图像传感器。由于CMOS图像传感器的不断普及,且由于机器视觉、电影制作、工业、汽车和扫描应用要求必须以高图像品质捕捉快速移动的物体,图像传感器供应商Aptina公司已经致力于克服在CMOS图像传感器上使用全局快门像素技术的相关传统障碍。在这种努力下,所提供的全局快门像素技术具有更小的像素尺寸、更大的填充系数、更高的GSE、更低的暗电流和更低的噪声,使得CMOS图像传感器在更多应用中成为CCD传感器的可行替代方案。

卷帘式快门技术概述

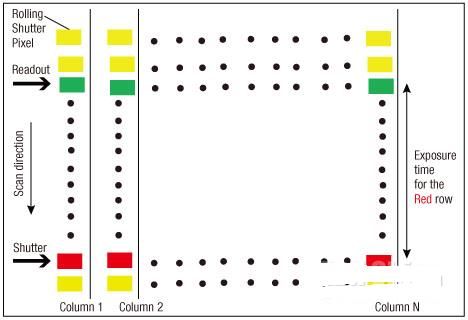

卷帘式快门也称为焦平面快门(focal-plane shutter),利用行复位和行读出(reset and readout)两个扫描来控制曝光时间。实现行复位的快门脉冲在行读出之前将某一行像素复位(如图1所示)。快门和读出脉冲的时间间隔决定了曝光时间。然而,在使用卷帘式快门传感器时,因为不同行的曝光是在不同时点进行的,因而拍摄快速移动物体的静态影像时会产生失真,这使得卷帘式快门不适合条形码读出、机器视觉或自动检验系统等应用,因为这些应用要求对快速移动物体进行成像。

图1,典型的卷帘式快门工作原理

人们经常在使用某些胶片摄影机以及CMOS数码相机和摄像机时发现,其中的卷帘式快门无法在单一时间点记录整个画面,而是通过垂直或水平扫描整个画面来捕获连续的像素条。卷帘式快门的优点是图像传感器可以在拍摄期间连续收集光子,这样增强了光感度。然而在运动或闪光等极端条件下成像时,卷帘式快门有明显的缺点:即快速移动物体或闪光带来的失真,比如模糊(smear)、扭曲、晃动和局部曝光。

在过去一段时间里,人们一直在探索如何从卷帘式快门转变到全局快门。但CMOS图像传感器供应商发现增加额外的存储单元将会牺牲太多的光敏(电二极管)区域,对量子效率产生负面影响。而且,出于对当时的半导体工艺技术、应用层面的要求、市场需求、成本和其它因素的考量,无法断定其产品可行性而未能有所进展。

全局快门技术概述

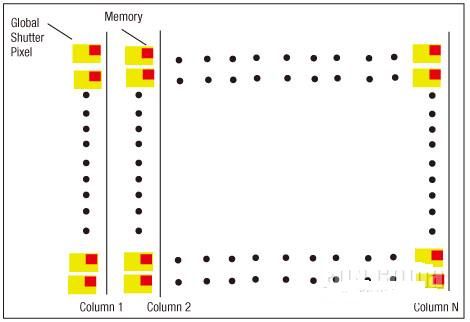

CCD图像传感器需要模拟存储器来进行工作,自然可以使用全局快门技术,因此采用全局快门技术的CCD相机及摄像机已相当普遍。全局快门通过同时捕获整个画面的图像来消除卷帘式快门伪像(如图2所示)。

图2,典型的全局快门工作原理。

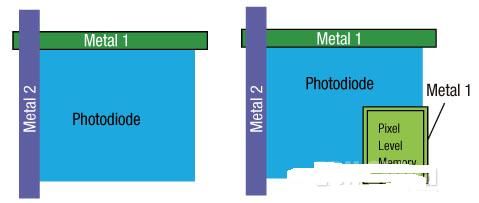

然而,对于CMOS图像传感器来说,全局快门实施方案的主要缺点是需要增加像素级存储器,对于某些应用,这使其成为比较昂贵的方案选择(如图3和图4所示)。

图3,卷帘式快门像素。 图4,全局快门像素。

以往全局快门技术的其它缺点还包括低填充-系数,这导致了量子效率的降低。为了补偿这一影响,全局快门像素的尺寸通常比卷帘式快门像素的尺寸大。

另一个重要问题就是存储节点的暗电流。暗电流指的是即便像素处于完全黑暗状态时像素中产生的微小电流。典型的暗电流产生区域包括PN结的耗尽区和硅片表面。暗电流是像素噪声的主要来源之一,并且在全局快门像素中比在卷帘式快门像素中更为严重。

- 图像传感器市场突破60亿美元,CMOS将占主导地位(05-22)

- 德国机器视觉产业增长显著,CCD/CMOS传感器产品前景看好(06-23)

- 美国Ziptronix对5层CMOS和光电二极管进行3维封装(03-18)

- CMOS成像技术让照相功能大显身手(07-01)

- 高速CMOS图像传感器及发展趋势(07-08)

- 市场趋于饱和,CMOS图象传感器已经日薄西山?(07-31)