利用直接数字频率合成技术提升无杂散动态范围性能

消信号与原始信号的组合。第二处则是增加一个乘法器,它以原始的频率调谐字作为一路输入,而以用户规定的频率缩放比例值作为另一路输入,这就提供了对对消信号的频率进行调节的能力。不过,因为对消信号的频率始终是原始频率的整数倍(如:谐波),乘法器的设计在一定程度上得以简化(采用整数而非浮点)。

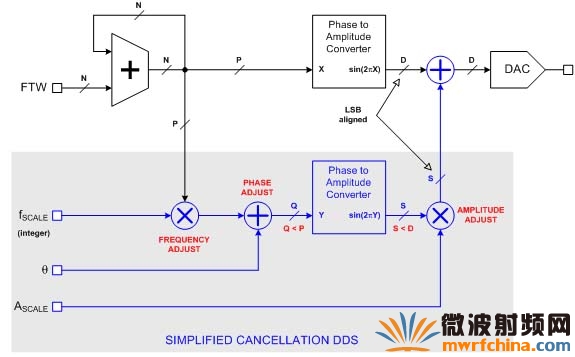

除了针对原DDS通道进行的两处改进之外,还需要对"对消"DDS进行两处修改(见图2)。第一是在累加器和相位-幅值转换器的之间插入一个加法器。这样,可以使对消信号相对于原始信号产生一个相位偏移(θ)。第二是在相位-幅值转换器的输出和DAC之前的加法器之间插入一个乘法器,这样能按比例调整对消信号的幅值。

图2

DDS产生的频率恰好为原始信号频率的整数倍的能力是相消干涉的重要因素。精确的频率匹配非常关键,否则谐波杂散信号和对消信号在相位上会出现相对漂移,使得相消干涉原理"遭到破坏"。

研究表明,对消DDS设计的复杂性可以低于原始DDS,这是因为,与原始信号相比,DAC产生的谐波杂散分量往往很小。一般来说,谐波杂散分量为-50dBc,或者更低。这样一来,对消信号的强度将不到DAC满量程输出的0.32%,这意味着,产生对消正弦信号时,并不需要用到DAC的高8位。于是,如果原始DDS设计中采用了一个14bit的DAC,则对消DDS只需要6bit的输出(14bit DAC分辨率减去8个未使用的高位)。相应的,这意味着对消DDS的相位-幅值转换器值需要具有9bit的相位分辨率。这基于DDS设计遵循的"经验法则"。因此,对对消DDS幅值需求的降低,意味着对消DDS所需的硬件要少于原始DDS。

经验法则:相位-幅值转换器的相位分辨率必须比其幅值分辨率高出至少3bit,以保证½LSB的幅值精度。

对消DDS还可以进一步简化。对消DDS累加器前的乘法器来产生所需要的谐波频率。不过,由于累加器只不过是一种累积相加的结构,而乘法与加法是可交换的,因此,乘法器也可以放置在累加器之后。因为原始信号和对消信号的累加器是并行工作的,对消累加器是冗余的,这使得对消DDS的结构更为简单,如图3所示。从图中还可看出,较小的输入和输出数据总线宽度(分别是Q和S)将使相位-幅值转换器变得更为简单。

图3

到目前为止,我们忽略了一个小问题。当原始和对消信号在到达DAC之前相加时,会出现溢出。这是因为,原始DDS的相位-幅值转换器的设计使之输出满量程正弦信号。任何添加到原始相位-幅值转换器满量程输出上的信号,都必然导致溢出。只需稍微衰减原始相位-幅值转换器的输出,使之为对消信号留出足够的空间,就可以轻松地解决这一问题,如图4所示。

图4

所要求的衰减取决于对消DDS能够产生的最大对消信号。最大对消信号基于S(在对消通道相位-幅值转换器的输出端处的数据总线宽度)。如果给定了一个D bit的DAC和一个最大宽度为S bit的对消信号,则所需的衰减值由下面的公式给出。例如,如果采用一个12bit的DAC和最大为4bit的对消信号,则衰减值为1-2(4-12)= 0.99609375。

只需要复制图2中所示的"简化的对消DDS",就可以非常简单地将该概念扩展为多通道的谐波抑制技术,如图4所示。请注意,每个对消DDS都有自己的频率、相位和幅值控制。所有对消通道在DAC之前与原始信号相加到一起。

图5

在多通道实现方案方面,需要注意的是余量调节所需的衰减值必须考虑到对消通道数量(N),因此对对消公式作轻微的调整:

用相消干涉方法消除谐波杂散分量时,实际需要的幅值和相位值取决于原正弦信号的频率和DAC内部的各种非线性特性。由于这种可变性的存在,对消DDS的幅值和相位设定必须根据经验来确定。

为了消除谐波杂散分量,首先应该确定其实际的频率。采样影响会导致所期望的谐波频率之外的频率点上出 现谐波杂散分量。其具体的频率点位置可以通过如下流程来确定。首先,令fS为DAC的采样速率,fP是原始正弦信号的频率,fH是谐波频率,而fSPUR是在对采样的影响进行修正后的谐波杂散分量的频率。为了找到fH,将fP乘以谐波数N(即,二次谐波N=2,三次谐波N=3)。接下来,求出fH / fS的余数R。如果R < fS/2,则fSPUR=R;否则,fSPUR=fS-R。

了解谐波杂散的确切位置后,就可以用频谱分析仪来确定其相对于原始正弦信号的幅值。注意杂散分量的幅值相对于原始信号的幅值的关系是以dBc为单位。例如,如果原始信号测量值为-12dB,而杂散分量的测量值为-71dB,则dBc值为-71-(-12)=-59dBc。于是,杂散分量和原始信号之间的电压关系即为:

因为原始信号的电压电平是DAC满量程摆幅输出决定,于是根据上面的比值,可得出所要

频率合成 相关文章:

- 基于FPGA和频率合成器的GPS信号源的设计(09-29)

- MAX2902与外部频率合成器结合使用方法(04-20)

- 基于ADF4106的锁相环频率合成器(08-07)

- 直接数字频率合成器设计(04-27)

- 利用7GHZ频率合成器实现快速锁定、高灵敏度的IF调谐无线接收机(05-30)

- 选择PLL频率合成器时,这些关键性能参数必须考虑(06-22)