无线射频收发系统硬件设计

引言

随着当今电子、计算机技术的飞速发展,射频技术作为一种无线网络通讯手段,已经在越来越多的场合上使用,并且表现出其独特的优越性。它取代了传统中错综复杂的电缆,使家庭或办公场所的移动电话、便携式电脑、打印机、复印机、键盘及其他设备实现了互联互通,将人们从无数的连接电缆中解放出来,自由方便地构成自己的个人网络。作为取代数据电缆的短距离无线通信技术,它将家庭或办公室中的各种数据和语音设备联成一个微微网,还可以进一步实现互联,形成一个分布式网络,从而在这些联接设备之间实现快捷而方便的通信联系,因此它在无线网络系统中的发展潜力巨大。

1 系统硬件组成与工作原理

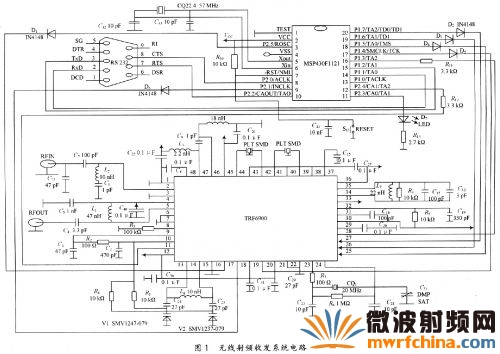

射频与数字基带部分电路通过合适的方式连接起来就构成了所设计的无线射频收发应用系统的硬件电路,总体电路如图l所示。其中,带有箭头的表示接外加的电压,以保证电路正常工作,其工作电压为3 V。

1.1 系统主电路结构与原理

射频部分电路主要是用TRF6900收发芯片和一些外围元件设计成的射频收发器。TRF6900是TexasInstruments公司推出的单片射频收发器芯片,其内部集成了完整的发射电路和接收电路。它的工作频率范围为850~950 MHz,供电电压范围为2.2~3.6 V,射频输出功率高达+5 dBm,而待机模式时的电流消耗仅在O.5~5μA之间。TRF6900采用高吞吐率16 bRISC结构,其最快速率可达8 MIPS。另外,这种收发器还具有FM/FSK调制模式,并采用三线制串行接口,因而能很方便地与微控制器相连接,可用于ISM频段内数据的双向无线传输,能够容易地对它的收发进行控制,因而基于它的应用也越来越普遍。

1.1.1 接收原理

从天线接收到的信号由LNA IN引入TRF6900,首先经过低噪音放大器。低噪音放大器提供13 dB的增益,它有正常和低增益两种模式,当TRF6900接收的信号较强时,应该选择低增益模式,这样可以最大程度地减少信号的非线性失真。放大后的信号被送入混频器,混频器将信号变频到中频,再通过第一和第二级中频放大。第一级中频放大可获得7 dB的增益,用以补偿滤波器带来的损耗;第二级中频放大包括多个放大器,总共可获得80 dB的增益。经过两级放大后的信号,如果采用的是FM/FSK调制方式,就送入FM/FSK解调器,解调出的数据信号从DATA OUT引出。如果是频移键控(ASK)或开关键控(OOK),则送入接收信号强度指示器(RSSI)解调,解调后的基带数据从RSSI OUT输出。

1.1.2 发射工作原理

数字基带信号从TX DATA引入TRF6900片内,经过直接数字频率合成器(DDS)调制到中频,再通过锁相环(PLL)倍频到射频,最后通过功率放大器放大信号后,由PA OUT导出射频信号,再通过天线发射出去。

1.1.3 串行控制接口工作原理

串行控制接口包括CLOCK,DATA,STOBE三部分,控制着TRF6900内部所有的寄存器,包括DDS参数设定寄存器和其他的控制寄存器。在CLOCK的每一个上升沿,DATA管脚的逻辑值送入24 b的移位寄存器,当STOBE电平被抬高时,设定的参数被送入选定的锁存器。TRF6900有四个可编程的24 b控制字(A,B,C,D)。控制字A和B分别控制DDS模式0和模式1状态下输出信号频率。控制字C负责锁相环和DDS模式O的设定。控制字D负责调制和DDS模式1的设定。

1.2数字基带部分

数字基带部分基于微型控制器MSP430F1121。通过它将外部的模拟信号转换为适合TRF6900的数字信号,再配合软件设计可以很方便地进行智能化转换。数字基带部分的硬件电路由RS 232和MSP430F1121组成,如图1所示。

MSP430F112l微型控制器是一款超低功耗、高性能的16位精简指令集MCU,主要由以下部分组成:基础时钟模块,包括1个数控振荡器(DCO)和1个晶体振荡器;看门狗定时器Watchdog Timer,可用作通用定时器;带有3个捕捉/比较寄存器的16位定时器Timer_A;2个具有中断功能的8位并行端口:P1与P2;模拟比较器Comparator A。

2 系统参数计算

2.1 鉴相器的参考频率

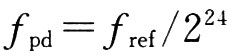

鉴相器是PPL构成锁相环中的单元模块之一,其输入的参考频率是由DDS的输出信号决定的。基于DSS技术的频率合成器能很好地满足各项指标性能,同时也使设计变得简单。鉴相器输出频率的分辨率为:

式中:fpd是鉴相器的最小输入频率,也是DDS时钟频率fref的2°,即最低有效位的权值。TRF6900 DDS累加器有24位,fpd乘以预标值N(可选择256或者512),由它可得出最小频率的步进值为:

累加器的输入是24位的用户串行数据(控制字),时钟基准信号作为累加器的工作时钟信号,两者决定频率的分辨率;输出是一串抽样斜坡数字脉冲,空号频率等于时钟频率。经过D/A转换后得到模拟域的正弦信号fo_DSS,它代表基准相位,即作为鉴相器的基准输入信号。DDS的最终性能主要取决于D/A转换过程中的量化误差以及滤波特性。

2.2 晶振时钟电路及频率

2.2.1 时钟电路的设计及参数计算

晶振采用并联谐振的工作方式,如图1中23~24脚外围电路所示。电路总的相移为360°,其中反向器提供180°的相移,R7和C22提供90°的滞后相位,晶振和电容C1也带来90°的相位滞后。并联工作的晶振是作为电感用的。晶振接入电容补偿相移以满足振荡条件。

偏振电阻R1用于设置反相器的偏置点,典型值是Vcc引脚值的二分之一。R1过小,将降低环路增益,破坏网络反馈条件,典型值是1~5 MΩ。可以观察23引脚的输出频率随电压的变化情况。如果晶振有过驱动,则增大电压后,输出频率会下降,此时应该微调电阻R2(调高)。注意,R2应该足够小,以确保振荡器在小于最小工作电压的情况下能够起振。C1和晶振的旁路电容Co及反相器的输入电容共同构成了晶振的输入电容。要提供稳定度,晶振的输入电容典型值可选择20~30 pF。