无线射频收发系统硬件设计

2.2.2 频率的选择

根据抽样定理可知,时钟频率fref(fref/2即为Na-quist频率)对量化噪声功率、冗余信号电平以及输出频谱中由于不满足抽样定理而带来的干扰信号、时钟频率和鉴相器的参考基准频率fo_DSS(即由DSS得到的信号频率fref/fo_DSS)的比率越大,频率合成器的输出信号频谱所受到的干扰就越少。时钟频率的具体计算方法如下:

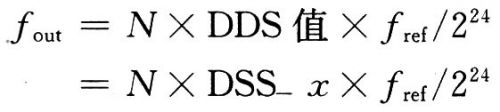

假设要使基于DDS的PLL构成的频率合成器的输出频率为906.24 MHz(与DSS得到的输出信号频率fo_DSS即鉴相器的参考基准频率要区别开来),经过256或者512分频(可选),假设为256,那么DDS的输出信号频率fo_DSS就应等于906.24/256=3.54 MHz,可得到PLL的输出频率的计算公式:

式中:预标值N可选择256或者512,DDS_x为控制字A或B的值。

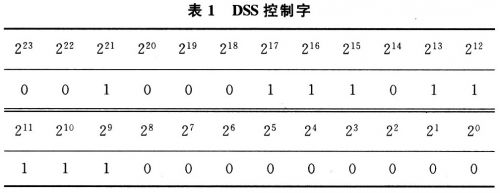

DSS频率值可通过串行口控制字编程设置,其最低有效位是2°,最高有效位是223。两个最高位(23,22位)用户不可访问,系统内部自动置为0,21-0位,并由用户编程设置。其中,A字对应DDS-O即模式0的频率;B字对应DDS-1即模式1的频率;C字控制PLL、数据限制器和模式1寄存器的设置;D字控制调制方式(如频偏大小)和模式O寄存器的设置。

2.3 载波频率计算

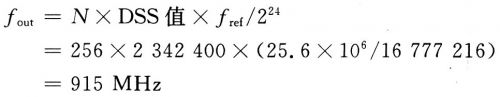

由时钟频率经过基于DDS的频率合成器可得到VCO输出的载波频率。对于典型的25.6 MHz时钟频率,由表1可得当DDS控制字为001,000,111,0000,000,000时,可计算出的VCO输出频率即载波频率为915 MHz。

由表1可知:

2.4 DSS控制字的计算

TRF6900的FSK调制是由专门的FSK频偏寄存器来完成。A,B控制字用来设置接收机和发射机的频率及信道。在应用系统的使用中,A,B控制字用来设置FSK频偏。用于FSK方式时DDS控制字的计算方法如下:

假设载波频率为915.O MHz,频偏为20 kHz,即A字对应的VCO输出频率fout1=915.00 MHz;B字对应的VCO输出频率fout2=915.02 MHz;时钟频率fclock=fref=25.6 MHz;分频比N=256。下面计算A,B控制字:

A字对应于DDS_O值:

所得的二进制的DDS_O将装入A控制字中。

B字对应于DDS_1值:

所得的二进制的DDS_1将装入B控制字中。

2.5 本地振荡器

TRF6900的本地振荡器(LO)是锁相环PLL形式,由基于片上DDS的频率合成器、低通滤波器(LPF)和压控振荡器(VCO)构成。

2.5.1 VCO的电路设计

压控振荡器是输出信号频率随输入控制电压变化的振荡器。为了减小相位噪声,VCO电路通常由分立元件构成。

LC谐振槽路的谐振频率:

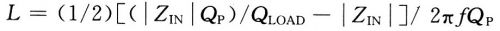

谐振频率时的电感值:

式中:|ZIN|为TRF6900内部振荡器的输入阻抗;QLOAD为谐振回路的品质因数;QP为电感的品质因数;f为谐振频率。

2.5.2 VCO的灵敏度

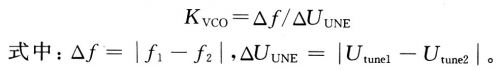

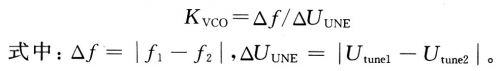

变容二极管的电容大小与调谐电压成正比,VCO的灵敏度:

2.5.3 参数计算

设计的无线收发电路工作在868~928 MHz ISM频段。假设TRF6900的VCO输出频率为880~950 MHz,调谐电压为0.3~2 V。TRF6900振荡器的输入阻抗|ZIN|即引脚13和14间的电阻大小约为1 400 Ω;谐振回路的品质因数必须大于等于10;在915 MHz时,电感的品质因数大约等于80。由公式可得:L≤10.65 nH,取L=10 nH标准值。

从方程中可知:

为了扩大变容二极管的调谐范围,根据以上的计算,C2可以取2.2pF,C1可取3.3pF。

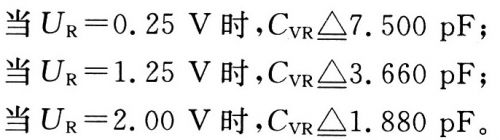

设计时采用Alpha Industries的SMV1247系列变容二极管,其参数如下:

要注意的是因为PCB的分布电容不可预测,随工作频率变化而变化,所以在PCB调试时要进行必要的修正,这里采用经验值。

现在对上述元件参数进行验证:

对于0.25 V时的ftune,依据公式有CTOTAL=3.346 pF;

对于2.00 V时的ftune,有CT0TAL=2.799 pF。

由上述方程式可知,槽路的谐振频率:MHz,,2 MHz。显然,能满足880~940 MHz频率调谐范围。对于满足880~940 MHz的频率调谐范围的元件参数,取L=10 nH,C1=3.3 pF,C2=2.2 pF,变容二极管为SMVl247-079。最后可得出VCO的灵敏度MHz/V。

2.5.4 环路滤波器的设计

(1)计算公式

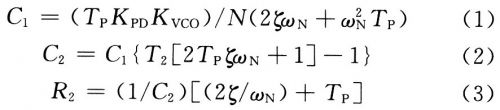

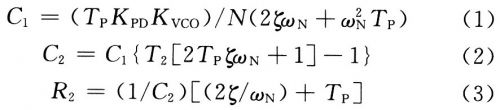

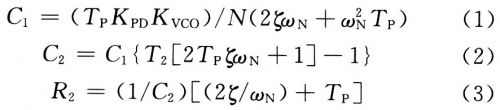

环路滤波器是一个典型的二阶低通滤波器,用于频率合成器中电荷泵电流模式。二阶元件的计算公式:

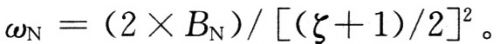

式中:KPD为鉴相器增益(单位:A/rad),KPD=ICP/2π;KVCO为VCO增益(单位:rad/V);N为分频比;ζ为阻尼比,有效范围是0<ζ<1,典型值为O.707;ωN为自然谐振频率(单位:rad/sec),ωN=(2×BN)/[(ζ+1)/2]2。

(2)设计注意事项

VCO有加速和正常两种工作模式,锁存时间都要小于250μs。正常模式用于精确控制并保持VCO工作所需频率;加速模式利用APLL锁相环加速因子来提供快速粗调,它可以使用TRF6900软件根据需要进行调整。DSS的谐振通常在环路带宽内,不能用环路滤波器抑制,但降低环路滤波的带宽可以减小DSS谐波产生的可能性。正确选择时钟基准频率能较好地抑制DSS谐波。