用于移动宽带基础设施的新一代无线电数字前端解决方案

ASSP一般适应市场需求的速度较慢,这在它们缺乏任何像CPRI或JESD204这样的串行接口技术可以看出。这就需要一个辅助器件,比如内置有串行解串器的FPGA或使用外部串行解串器的低成本FPGA来完善设计。但这种设置需要大量的组件,从而导致PCB占位面积大,电源高度复杂,总功耗和成本都很高。

图3所示的Zynq EPP采用双ARM® Cortex™-A9处理器内核(每个内核的整数运算性能高达2000MIPS)和一个双精度浮点单元。处理器子系统包含存储器控制器、千兆位以太网、UART和SPI/I²C等专用通信外设。紧邻处理器子系统的是高性能可编程逻辑,其内含500MHz DSP模块、12.5Gbps串行解串器和大量的内部RAM。多条低时延、高带宽总线用于连接处理器子系统和可编程逻辑,同时共享存储器接口可保证避免发生性能瓶颈。

图4所示的是设备制造商如何利用Zynq实现当今远程无线电装置中的全部功能。

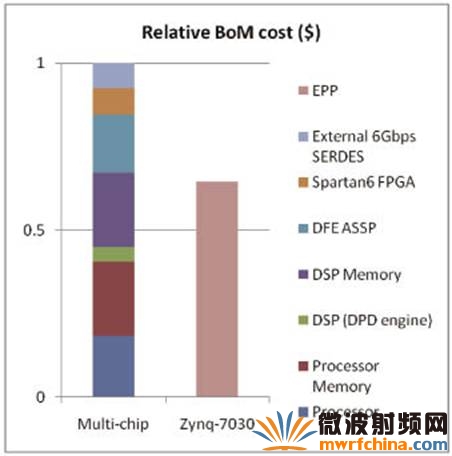

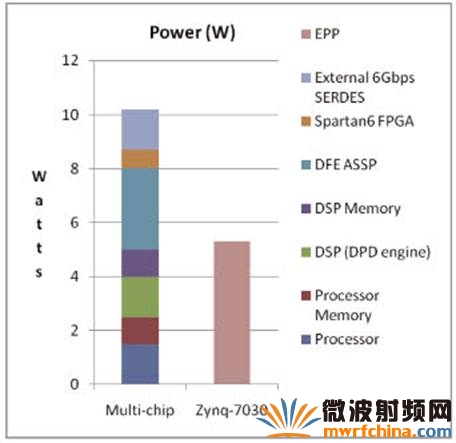

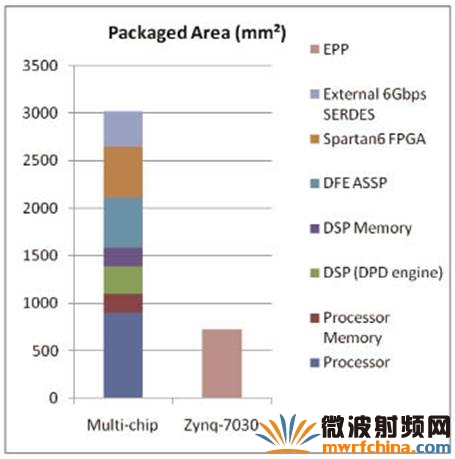

从图5和图6可以看出与现成的ASSP相比,这种架构能够实现明显的成本和功耗节约。这个示例假定信号带宽为20MHz,有两个发送和两个接收路径。Zynq还能够支持更高的带宽和更多数量的天线。

在2x2 20MHz LTE示例中,Zynq解决方案将功耗降低了高达50%,总材料成本相对等效ASSP设计降低了35%~40%。另外,图7还显示,由于较图2元组件数量减少,在提供图4中相同的功能时,封装面积可缩减达66%。

图5 使用Zynq相对降低材料清单(BOM)成本

图6 使用Zynq降低耗电

图7 使用Zynq缩减封装面积

使用Zynq还可以降低电源的复杂性和成本,同时提高无线电单元的可靠性。可靠性的提高能够减少对市场退货相关的后期执行费用的影响,还能够实现更高的网络可靠性。另外降低功耗还能够减少散热,从而可以使用尺寸更小、重量更轻的散热器和机械结构。最后,Zynq解决方案能够结合软硬件灵活性,在设计后期才确定无线电单元的规范。这样可以缩短产品上市时间,降低风险,在设备出货后很长时间内还能支持新功能。

- 现代无线电接收机的系统噪声系数分析二:Y因子噪声因子测量法(07-03)

- 现代无线电接收机的系统噪声系数分析一:级联接收机的计算(07-01)

- 零中频架构在无线电设计中的优势(05-30)