基于QDR-IV SRAM实现高性能网络系统设计

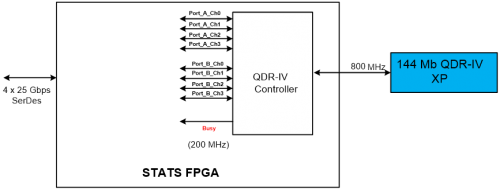

随机的。QDR-IV XP分为8个内存条,在一个周期内同一源地址不能有两次访问。因此,为避免出现访问内存条的冲突,存储控制器会发送控制流到统计更新逻辑单元。图3显示的是基于FPGA的内存控制器实例。在FPGA中,QDR-IV的每个800 Mhz端口都分成4个通道,每个通道都运行在200 MHz。

图3:基于FPGA的QDR-IV存储控制器

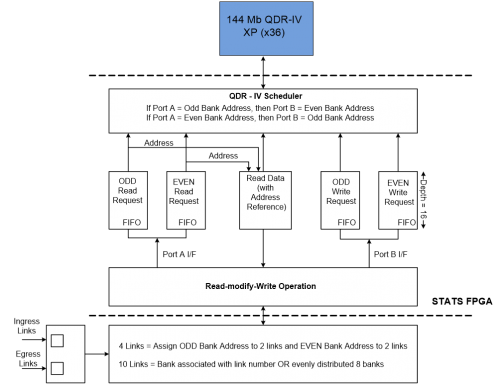

当端口A和B之间出现访问内存条的冲突时,存储控制器将发出"忙碌"(Busy)信号,并将违反的存取操作顺延至下一个时钟周期。如出现"忙碌"信号,系统将不再响应更新率请求。这一问题可通过系统地将计数器分配到它们的存储器阵列地址来解决。QDR-IV有8个内存条,由3个存储地址LSB(最低有效位)表示。对于当前的例子而言,QDR-IV地址的LSB A【0】被映射到上行(入端口)(A【0】=1】)和下行(出端口)(A【0】=0】),以便形成用于调度的奇数和偶数地址。以下图4是假定上行和下午计数器均不超过4亿次更新/秒的情况下,如何实现用于统计更新功能的存储子系统。

图4:基于极速性能QDR-IV的统计计数器解决方案

传入的数据包,以及对应的计数器,自动分为几类。这些计数器类别需要分配不同的内存条,以便避免内存条冲突,并充分发挥QDR-IV XP存储器的性能。根据整体系统架构的不同,分类如下:

1、 基于上行或下行的计数器分类

2、 如果多个NPU(网络处理器)连入同一个统计计数器FPGA,则每个NPU需分配一个不同的内存条

3、 基于以太网连接的计数器分类和内存条分配

4、 基于虚拟通道(VL)或服务等级(CoS)的计数器分类和存储器阵列库分配

5、 基于流的计数器分类和适当的内存条分配

6、 用于定制方案的其它数据包/计数器分类法

结论

QDR-IV SRAM的高随机存取速率使其非常适合高性能要求的网络应用。本文介绍了使用QDR-IV HP和QDR-IV XP用于转发表查找和统计计数器应用实例。系统架构师和设计师可以参照这些例子开始自己的设计,并根据具体的应用需要进行改动。QDR-IV HP和QDR-IV XP均得到了Altera公司和Xilinx公司的存储控制器IP的支持,使存储子系统支持100G到400G的线卡。

- 赛普拉斯的低功耗无线解决方案可助PURE 音频系统智能连接(05-12)

- AGIG采用最高密度、无需电池的非易失性RAM系统(09-23)

- 2010 FIRST机器人大赛选用赛普拉斯PSoC3 FirstTouch入门套件(02-13)

- 使用QDR-IV设计高性能网络系统之一(01-16)

- 使用QDR-IV设计高性能网络系统之三(01-22)

- 网络通信与便携式应用驱动SRAM技术(07-28)