网络通信与便携式应用驱动SRAM技术

时间:07-28

来源:互联网

点击:

数据通信和便携式系统成为当今SRAM的重要应用领域。某些SRAM由于能够提供实现较高带宽所需的性能(比如在网络系统中)或维持较长电池使用寿命所需的低功耗(比如在便携式设备中)而在许多应用中起着主导作用。这些架构指的是面向高性能应用的NoBL(无总线延迟)和QDR(四倍数据速率)以及针对低性能应用的MoBL(更长的电池使用寿命)。

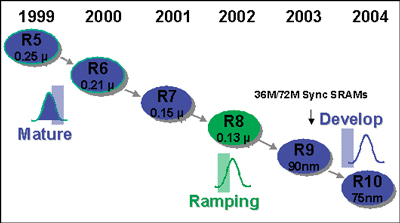

多年来工艺几何尺寸的不断压缩使得兼顾速度、功耗和密度的新型架构的推出成为可能。以赛普拉斯为例,目前已可提供采用90nm制造工艺的72Mbit密度的标准同步/NoBL SRAM器件样品。

不断缩小的工艺几何尺寸使得各家公司能够在存储器技术上确立诸多优势,如实现更快的速度、更低的功耗、更高的存储密度和更有竞争力的制造成本。

网络与数据通信领域竞速

在当今的网络应用中,分组处理需要极高的存储带宽。分组处理所涉及的多项功能再加上其他的存储功能对SRAM提出了不同的要求。人们已经开发出了所需的SRAM用新型协议和架构,以便对数据通信系统的需要提供支持。

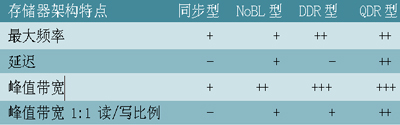

目前,网络系统中采用了多种同步SRAM架构,包括流水线突发型、直通型、无总线延迟(NoBL)(流水线/直通)型、双倍数据速率(DDR)型SRAM和四倍数据速率(QDR)型SRAM等等。

同步流水线型和直通型SRAM面市已有很多年了,它们最初是为PC高速缓存应用而开发的。现今一般用于低性能网络领域,主要目的在于实现成本-效益性。流水线型和直通型SRAM的主要缺陷是其需要在读写操作的转换期间插入空闲周期。对于要求进行快速随机交替读写存储器存取操作的网络应用而言,这两种架构的效率不够高。

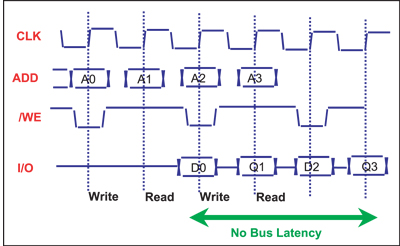

而NoBL架构通过免除在读写操作之间插入空闲周期的需要而实现了100%的利用率,从而增加了总带宽。NoBL SRAM支持流水线型和直通型操作。采用流水线型NoBL时,写数据被延迟两个周期;采用直通型NoBL时,则写数据被延迟一个周期。由于写数据被延迟,因此免除了插入空闲周期的需要,从而可为连续或随机读/写操作提供相同的带宽。图2示出了一种用于流水线型NoBL SRAM的简单读/写存取。

NoBL SRAM作为同步流水线型和直通型SRAM的一种快速替代方案而被高性能网络应用设计所采用。由于从同步型转变为NoBL型只需对控制器逻辑稍做修改,所以向NoBL SRAM的过渡相对容易。市面上还有其他一些类似的架构选择方案:如NtRAM和ZBT。

而上面讨论的同步架构均为单数据速率,在这种架构中,数据和控制信号是在时钟脉冲的上升沿被触发的,而且,数据的一个字在每个时钟脉冲的上升沿进行传送。

为了获得更高的数据传送速率并最大限度地增加吞吐量,人们开发出了双倍数据速率(DDR)SRAM。DDR器件在时钟脉冲的上升沿和下降沿上均传送数据。

DDR/QDR SRAM是面向下一代高速网络应用(例如工作于200MHz以上的数据速率条件下的交换器和路由器)的高性能SRAM架构。

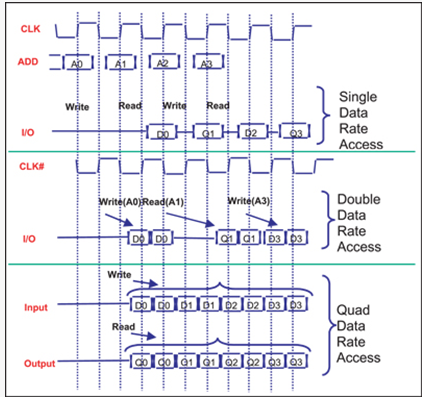

图3示出了用于单数据速率(SDR)、双倍数据速率(DDR)和四倍数据速率(QDR)的读/写存取。对于数量对称的读写操作很明显,在相同的频率和I/O总线宽度条件下,QDR可提供最高的带宽。

便携式领域“变型”

便携式产品及其他的低功耗应用需要采用具有超低功耗的存储器。为了对这些便携式应用的需要提供支持,人们引入了各种现有的和新型的架构。便携式产品中,对增加新功能以及支持更高数据速率和附加话音功能方面需求最旺盛的当属移动电话。这对主要存储器技术针对便携式产品需求的诸多变革起到了推波助澜的作用。

目前便携式系统可用的存储器类型为标准6T SRAM(MoBL1、MoBL2)、伪SARM(MoBL3、CellularRAM)和SDRAM(MoBL4)。图4概括了存储器的发展历程。

MoBL1/2为标准6T SRAM。它们的优点在于具有非常低的工作和待机电流。这些SRAM还具有宽工作电压范围。高速操作和低待机功耗是6T SRAM的重要特性。赛普拉斯公司的MoBL1和MoBL2器件甚至允许在低至1.0V的电压条件下进行数据保存。

随着移动设备所提供的应用越来越多,处理能力方面的要求正在不断提高,同时还需要采用存储容量更大的存储器。由于SRAM不能适应移动通信行业日益提高的需要,因此,伪SRAM再度进入人们的视线。这种存储器具有用于模拟SRAM操作的DRAM内核及附加逻辑电路。

赛普拉斯公司提供的MoBL3系列PSRAM把从低功耗SRAM的设计和开发中获得的知识引入到了DRAM中。这些器件的构成形式使得能够对刷新进行内部控制,并在标准SRAM存取过程中进行调节。

与同档次的SRAM相比,大多数PSRAM的待机电流都较高。造成这种现象的原因在于必须定期完成内部刷新周期以保持存储器中的数据完整性。赛普拉斯公司的MoBL3器件采用了温度控制型刷新电路,这使得存储器能够在较低的工作温度下降低刷新要求,从而减小待机电流。MoBL3器件还引入了一种所谓“部分阵列刷新”的概念,使得用户能够关闭存储器的某些未用部分,以便进一步减小刷新电流。大多数MoBL3器件具有约100μA的最坏情况待机电流和50μA左右的典型待机电流。MoBL3器件还提供了另一种被称为“深度睡眠模式”的工作方式,它使得用户可在存储器未执行任何操作的时候将存储器阵列关闭。

多年来工艺几何尺寸的不断压缩使得兼顾速度、功耗和密度的新型架构的推出成为可能。以赛普拉斯为例,目前已可提供采用90nm制造工艺的72Mbit密度的标准同步/NoBL SRAM器件样品。

不断缩小的工艺几何尺寸使得各家公司能够在存储器技术上确立诸多优势,如实现更快的速度、更低的功耗、更高的存储密度和更有竞争力的制造成本。

图1:赛普拉斯公司SRAM工艺技术发展走势图(0.25μm至90nm)

网络与数据通信领域竞速

在当今的网络应用中,分组处理需要极高的存储带宽。分组处理所涉及的多项功能再加上其他的存储功能对SRAM提出了不同的要求。人们已经开发出了所需的SRAM用新型协议和架构,以便对数据通信系统的需要提供支持。

目前,网络系统中采用了多种同步SRAM架构,包括流水线突发型、直通型、无总线延迟(NoBL)(流水线/直通)型、双倍数据速率(DDR)型SRAM和四倍数据速率(QDR)型SRAM等等。

同步流水线型和直通型SRAM面市已有很多年了,它们最初是为PC高速缓存应用而开发的。现今一般用于低性能网络领域,主要目的在于实现成本-效益性。流水线型和直通型SRAM的主要缺陷是其需要在读写操作的转换期间插入空闲周期。对于要求进行快速随机交替读写存储器存取操作的网络应用而言,这两种架构的效率不够高。

图2:用于流水线型NoBL SRAM的简单读/写存取

而NoBL架构通过免除在读写操作之间插入空闲周期的需要而实现了100%的利用率,从而增加了总带宽。NoBL SRAM支持流水线型和直通型操作。采用流水线型NoBL时,写数据被延迟两个周期;采用直通型NoBL时,则写数据被延迟一个周期。由于写数据被延迟,因此免除了插入空闲周期的需要,从而可为连续或随机读/写操作提供相同的带宽。图2示出了一种用于流水线型NoBL SRAM的简单读/写存取。

NoBL SRAM作为同步流水线型和直通型SRAM的一种快速替代方案而被高性能网络应用设计所采用。由于从同步型转变为NoBL型只需对控制器逻辑稍做修改,所以向NoBL SRAM的过渡相对容易。市面上还有其他一些类似的架构选择方案:如NtRAM和ZBT。

而上面讨论的同步架构均为单数据速率,在这种架构中,数据和控制信号是在时钟脉冲的上升沿被触发的,而且,数据的一个字在每个时钟脉冲的上升沿进行传送。

为了获得更高的数据传送速率并最大限度地增加吞吐量,人们开发出了双倍数据速率(DDR)SRAM。DDR器件在时钟脉冲的上升沿和下降沿上均传送数据。

DDR/QDR SRAM是面向下一代高速网络应用(例如工作于200MHz以上的数据速率条件下的交换器和路由器)的高性能SRAM架构。

为了避免发生总线争用;公用I/O总线也被分割成两根总线;分别用于对四倍数据速率(QDR)SRAM进行读取和写入操作。

图3:SDR/DDR/QDR读/写存取的比较

图3示出了用于单数据速率(SDR)、双倍数据速率(DDR)和四倍数据速率(QDR)的读/写存取。对于数量对称的读写操作很明显,在相同的频率和I/O总线宽度条件下,QDR可提供最高的带宽。

便携式领域“变型”

便携式产品及其他的低功耗应用需要采用具有超低功耗的存储器。为了对这些便携式应用的需要提供支持,人们引入了各种现有的和新型的架构。便携式产品中,对增加新功能以及支持更高数据速率和附加话音功能方面需求最旺盛的当属移动电话。这对主要存储器技术针对便携式产品需求的诸多变革起到了推波助澜的作用。

目前便携式系统可用的存储器类型为标准6T SRAM(MoBL1、MoBL2)、伪SARM(MoBL3、CellularRAM)和SDRAM(MoBL4)。图4概括了存储器的发展历程。

MoBL1/2为标准6T SRAM。它们的优点在于具有非常低的工作和待机电流。这些SRAM还具有宽工作电压范围。高速操作和低待机功耗是6T SRAM的重要特性。赛普拉斯公司的MoBL1和MoBL2器件甚至允许在低至1.0V的电压条件下进行数据保存。

随着移动设备所提供的应用越来越多,处理能力方面的要求正在不断提高,同时还需要采用存储容量更大的存储器。由于SRAM不能适应移动通信行业日益提高的需要,因此,伪SRAM再度进入人们的视线。这种存储器具有用于模拟SRAM操作的DRAM内核及附加逻辑电路。

赛普拉斯公司提供的MoBL3系列PSRAM把从低功耗SRAM的设计和开发中获得的知识引入到了DRAM中。这些器件的构成形式使得能够对刷新进行内部控制,并在标准SRAM存取过程中进行调节。

与同档次的SRAM相比,大多数PSRAM的待机电流都较高。造成这种现象的原因在于必须定期完成内部刷新周期以保持存储器中的数据完整性。赛普拉斯公司的MoBL3器件采用了温度控制型刷新电路,这使得存储器能够在较低的工作温度下降低刷新要求,从而减小待机电流。MoBL3器件还引入了一种所谓“部分阵列刷新”的概念,使得用户能够关闭存储器的某些未用部分,以便进一步减小刷新电流。大多数MoBL3器件具有约100μA的最坏情况待机电流和50μA左右的典型待机电流。MoBL3器件还提供了另一种被称为“深度睡眠模式”的工作方式,它使得用户可在存储器未执行任何操作的时候将存储器阵列关闭。

- 热插拔和缓冲I2C总线 (04-14)

- PCIe总线何时突破Unix服务器坚冰(02-03)

- TMS320VC5402 HPI接口与PCI总线接口设计(04-12)

- 基于Nios II的I2C总线接口的实现(04-09)

- 双口RAM CY7C026在高速数据采集系统中的应用(04-12)

- 计算机在新型多电机同步系统中的应用(07-08)