基于QDR-IV SRAM实现高性能网络系统设计

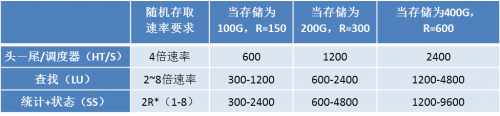

尾高速缓存的调度器数据库进行高效寻址。 表1显示了一个路由器中不同存储子系统的随机存取速率要求,单位为百万次存取/秒(MT/s)。R是数据包速率,单位为百万数据包/秒(Mpps)。

表1:路由器不同功能所需的存储器RTR要求

QDR-IV SRAM概述

QDR-IV SRAM配备了一个同步接口,可在一个时钟周期内完成两次写操作或两次读操作,或一次读写结合的操作。QDR-IV有两个双向数据端口A和B,每个均可以用于读或写操作。这一特点带来了额外的灵活性,架构师可将之用于读/写并不一定平衡的应用中。每个端口在两个时钟沿均可进行数据传输(DDR(双倍数据速率)操作),工作模式为突发式,每个时钟周期的突发长度为两个字(每个字为X18或X36)。地址总线为通用型,同样支持双倍数据速率,其上升沿和下降沿能分别为端口A和端口B提供地址。QDR-IV支持嵌入式ECC(错误检查和纠正),可从根本上消除软错误,提高存储器陈列的稳定性。

QDR-IV SRAM有两种规格,即QDR-IV HP和 QDR-IV XP。HP的频率最高可运行在667 MHz,而XP存储器则可高达1066 MHz。下表列出了两种QDR-IV的关键结构特点。两种存储器均有72和144 Mbs两种密度可选,并且支持密度或性能的宽度和深度扩展。

表2:QDR-IV SRAM的主要功能

QDR-IV HP 和XP的主要区别是内存条(bank)的使用。QDR-IV XP可通过将存储器空间分成8个内存条来增加性能,用3个地址的最低有效位(LSB)表示。要求的存储方案是在同一周期内存取不同的内存条。从一个周期到另一周期,所有的内存条均可存取,系统设计师可通过规划系统架构来相应地分配记忆库地址,充分发挥极速存储器的RTR性能。

以下例子展示了两种应用,一种使用QDR-IV HP来进行转发表查找,而另一种将QDR-IV XP用于统计计数器,线路速率均为400Gbps。

400Gbps线速下的转发表查找

如前所述,转发表查找需要任何地方均为2R到8R的存取,此处R为包速率,单位为百万数据包/秒(Mpps)。在400Gbps的线速下,R=600,要求RTR为1200到4800MT/s。以符合以下转发表要求的400Gbps二层交换机为例:

1M x 144位条目

每个数据包查找1个目标地址(DA)(读取)

每个数据包查找1个源地址(SA)(读取)

1次源地址登记(写)或60 Mpps下的CPU访问

基于以上:

密度要求:1M x 144位 => 144 Mb

读访问速度(目标地址+源地址) = 600 +600 = 1200 Mpps

写入更新速率 = 60Mpps

由于数据总线为读写共用,当读操作后续为写操作时,总线需要调转方向。因此,QDR-IV高性能SRAM每次从读到写的切换需要4个周期。因时延的缘故,从写到读不会出现这种情况,读取有5个时延周期,而写入仅有3个时延周期。因总线转向而导致的带宽损失可通过在写入查找表前,最多4次刷新先进先出(FIFO)队列来尽可能地减少。因此需要FIFO中带有一个最新条目的4排高速缓存,如果地址匹配的话此缓存可提供源地址或目标地址查找。每次写入更新的内部整理自检为:

= 4个写入周期 + 4个总线转向周期/4个周期

= 2

用于写入更新的RTR = 写入的内部整理自检* 写入的更新率

= 2 * 60 = 120Mpps速率。

整体RTR要求 = 600+600+120 = 1320MT/s

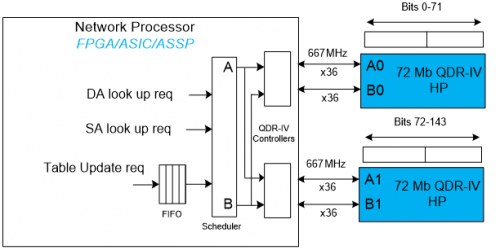

以下是使用两个72Mb, X36 QDR-IV HP的存储子系统(运行频率为667Mhz)。这两个QDR存储组成带宽扩展模式,以便每个时钟周期在端口【A0、A1】和端口【B0、B1】支持144bits的数据。调度器在目标地址、源地址读取请求和表写入请求(一次性4次写入)之间做出判断,并将它们发送到端口【A0、A1】或端口【B0、B1】。有足够的带宽来满足所有的请求。通过附加QDR-IV HP存储器进行深度和宽度扩展,还能支持更多的表条目,或支持每条目更多位数。

图2:使用QDR-IV HP的转发表查找

400Gbps的统计计数器

如前所述,统计计数器需要任何地方均为2R到16R的存取,此处R为包速率,单位为百万数据包/秒(Mpps)。在400Gbps的线速下,R=600,要求RTR为1200到9600MT/s。以符合以下统计计数器要求的路由器为例:

上行为1百万计数器对

下行为1百万计数器对

每计数器对72bits

每秒8亿次更新

密度要求:2 M x 72 = 144 Mb

要求的RTR = 1600 MT/s(由于读取-修改-写入操作的原因,为2x数据包更新速率)

一个工作在800Mhz的极速X36 QDR-IV存储器即可满足此要求。SRAM的每个存储位置存储两个计数器,每个36 bits,总共200万个计数器。一个典型的计数器对是"总收到的数据包数"和"总字节数",能很容易地保存在SRAM的地址单元内。端口A用于读取操作,端口B用于写入操作,因此无需总线转向时间。

由于传入包的随机性,计数器更新访问的地址也是

- 赛普拉斯的低功耗无线解决方案可助PURE 音频系统智能连接(05-12)

- AGIG采用最高密度、无需电池的非易失性RAM系统(09-23)

- 2010 FIRST机器人大赛选用赛普拉斯PSoC3 FirstTouch入门套件(02-13)

- 使用QDR-IV设计高性能网络系统之一(01-16)

- 使用QDR-IV设计高性能网络系统之三(01-22)

- 网络通信与便携式应用驱动SRAM技术(07-28)