使用QDR-IV设计高性能网络系统之一

时间:01-16

来源:3721RD

点击:

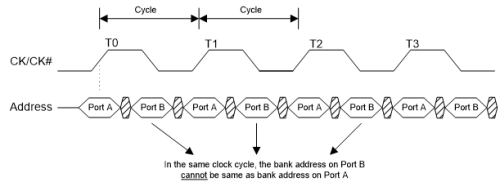

XP SRAM – 写/读操作

在相同的时钟周期内,端口B上的组地址与端口A上的组地址不相同

图5. QDR-IV HP SRAM –写/读操作

QDR-IV XP SRAM 上的分组限制可作为某些应用的一个优点,在这些应用中,存储器中的每一组都有不同的用途,并且都不能在同一个时钟周期中被访问两次。一个网络路由器能够在QDR-IV XP SRAM 的每一组内储存不同的路由表便是一个实例。如果在同一个时钟周期内特定的路由表仅能被访问一次,则有可能实现高TRT (随机数据传输速率)。在该情况下,工作频率为1066 MHz 时,可获得的最高随机数据传输速率为2132 MT/s。

分组限制不会影响到数据传输速率的另一种情况是使用物理层上的多个端口进行设计,通过每一个端口可以直接访问存储器中一组。这些端口将被复用到QDR-IV XP SRAM 的端口A 和端口B。在该设计中,因为每一个组都连接了物理层上不同的端口,因此任何一个组都不能在同一个时钟周期内被访问两次。

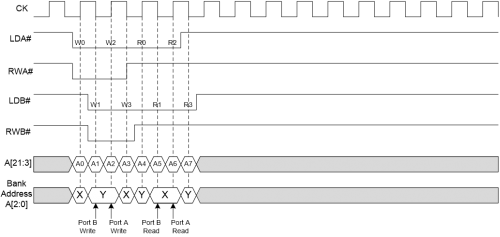

不过,如果第一次访问某一组是通过当前时钟周期的下降沿上端口B 进行的,并且第二次访问则是通过下一个时钟周期的上升沿上端口A 进行的,那么可以在一个时钟周期内再次对同一组进行访问。如图6所示,在进行写操作期间,端口B 和端口A 都可以在一个时钟周期内访问组Y。同样,在进行读操作期间,端口B 和端口A 可以在一个时钟周期内访问组X。

图6. 在一个时钟周期对同一个存储器组进行访问

在本系列第二部分,我们将探讨总线转换、总线翻转、地址奇偶校验等重要的总线问题。

- 赛普拉斯的低功耗无线解决方案可助PURE 音频系统智能连接(05-12)

- AGIG采用最高密度、无需电池的非易失性RAM系统(09-23)

- 2010 FIRST机器人大赛选用赛普拉斯PSoC3 FirstTouch入门套件(02-13)

- 基于QDR-IV SRAM实现高性能网络系统设计(01-16)

- 使用QDR-IV设计高性能网络系统之三(01-22)

- 网络通信与便携式应用驱动SRAM技术(07-28)