使用QDR-IV设计高性能网络系统之一

度配置,表2显示了输入时钟与输入写数据之间的关系。为了确保指令和数据周期的正确时序,并确保正确的数据总线返回时间,DKA/DKA#和DKB/DKB#时钟必须符合各自数据表中给出的CK to DKx斜率 (tCKDK)。

表2. 输入时钟与写数据之间的关系

| 输入时钟 | x18 | x36 |

| DKA0/DKA0# | Controls DQA[8:0] | Controls DQA[17:0] |

| DKA1/DKA1# | Controls DQA[17:9] | Controls DQA[35:18] |

| DKB0/DKB0# | Controls DQB[8:0] | Controls DQB[17:0] |

| DKB1/DKB1# | Controls DQB[17:9] | Controls DQB[35:18] |

QKA/QKA#和QKB/QKB#是与读取数据相关联的输出时钟。这些时钟与输出读取数据边沿对齐。

QK/QK#是数据输出时钟,由内部锁相环(PLL)生成。它与CK/CK#时钟同步,并符合各自数据表中给出的CK to QKx斜率 (tCKQK)。

根据QDR-IV SRAM器件的数据总线带宽的配置情况,表3显示了输出时钟与读取数据之间的关系。

表3. 输出时钟与读取数据之间的关系

| 输出时钟 | x18 | x36 |

| QKA0/QKA0# | Controls DQA[8:0] | Controls DQA[17:0] |

| QKA1/QKA1# | Controls DQA[17:9] | Controls DQA[35:18] |

| QKB0/QKB0# | Controls DQB[8:0] | Controls DQB[17:0] |

| QKB1/QKB1# | Controls DQB[17:9] | Controls DQB[35:18] |

读/写操作

读和写指令由控制输入(LDA#、RWA#、LDB#和RWB#)和地址输入驱动。在输入时钟(CK)的上升沿上对端口A控制输入进行采样。在输入时钟的下降沿上对端口B控制输入进行采样。

表4显示的是端口A和端口B的读/写操作条件。

表4. 端口A和端口B的读/写条件

|

| 读操作 | 写操作 |

| Port A | LDA# = 0和RWA# =1 | LDA# = 0和RWA# =0 |

| Port B | LDB# = 0和RWB# =1 | LDB# = 0和RWB# =0 |

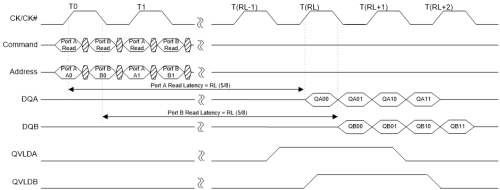

如图2 和图3 所示,对于QDR-IV HP SRAM,端口A的读取数据在CK的上升沿后整五个读取延迟(RL)时钟周期后才从DQA 引脚上输出;对于QDR-IVXP SRAM,则需要八个读延迟(RL)时钟周期。CK信号的上升沿发生,同时读取指令发出,经过指定的RL时钟周期后才可获取数据。

对于QDR-IV HP SRAM,端口A的写入数据在CK的上升沿后整三个写入延迟(WL)时钟周期才传输至DQA 引脚;对于QDR-IV XP SRAM,则需要五个写延迟(WL) 时钟周期。CK信号的上升沿发生,同时写入指令发出,经过指定的RL时钟周期后才可获取数据。

对于QDR-IV HP SRAM,端口B的读取数据在CK的上升沿后整五个RL 时钟周期才从DQB引脚上输出;对于QDR-IV XP SRAM,则需要八个RL 时钟周期。CK信号的上升沿发生,同时读取指令发出,经过指定的RL时钟周期后才可获取数据。

对于QDR-IV HP SRAM,端口B的写入数据在CK的上升沿后整三个WL 时钟周期才传输至DQB引脚;对于QDR-IV XP SRAM,则需要五个WL 时钟周期。CK信号的上升沿发生,同时写入指令发出,经过指定的RL时钟周期后才可获取数据。

QVLDA/QVLDB 信号表示相应端口上的有效输出数据。在总线上驱动第一个数据字的半周期前置位QVLDA 和QVLDB信号,并在总线上驱动最后一个数据字的半周期前取消置位它们。最后数据字后的数据输出是三态的。

图2. 读取时序

图3. 写时序

旨在实现高速运行的分组操作

QDR-IV XP SRAM 的设计是为了支持频率更高的八组模式(最大工作频率 = 1066 MHz),而QDR-IV HP SRAM 则支持频率较低的无分组模式(最大工作频率 = 667 MHz)。

QDR-IV XP 中较低的三个地址引脚(A2、A1 和A0)选择了在读或写期间将要访问的组。唯一的分组限制是在每个时钟周期内该组仅能被访问一次。QDR-IV XP SRAM 的组访问规则要求在端口B 上访问的组地址与在端口A 上访问的组地址不相同。

如果不符合分组限制,那么由于在时钟的上升沿时已经对读/写操作进行采样,在端口A 上则不会限制读/写操作,但会禁止端口B 上的读/写操作。QDR-IV HP SRAM 并没有任何分组限制。

图4. QDR-IV

- 赛普拉斯的低功耗无线解决方案可助PURE 音频系统智能连接(05-12)

- AGIG采用最高密度、无需电池的非易失性RAM系统(09-23)

- 2010 FIRST机器人大赛选用赛普拉斯PSoC3 FirstTouch入门套件(02-13)

- 基于QDR-IV SRAM实现高性能网络系统设计(01-16)

- 使用QDR-IV设计高性能网络系统之三(01-22)

- 网络通信与便携式应用驱动SRAM技术(07-28)