一种突发直扩接收机的快速载波同步方案

0 引言

突发扩频通信技术因其具有很强的抗干扰和抗截获能力,近年来成为军事领域研究的热点。其本质是在突发通信技术的基础上,对收发信号分别进行扩频和解扩,以进一步增加信号的保密性。扩频前的一帧典型突发信号结构为一段导频序列加上一段携带信息的用户数据。

为了实现对一帧突发信号的正确解调,要在解扩出符号数据后,在规定的导频序列长度内通过有限次调整完成载波同步,否则将造成后续用户数据的丢失,导致解调失败。FLL(锁频环)+PLL(锁相环)是一种常用的,可以校正大频偏的载波同步算法,但它常用于对同步时间要求不高的连续通信系统,用于本文所涉及的突发通信系统时,经过仿真发现所需要的环路调整次数大于导频序列长度,收敛速度不够快,无法满足指标,所以对该算法进行了一些改进,通过先使用一部分的导频序列进行FFT校频,快速减小频偏,然后用FLL将频偏缩小到10 Hz以内,最后用PLL来精确锁定。

1 快速同步算法设计

在发射端设计的一帧发射信号为168 b全0导频序列+132 b用户数据共300 b,如图1所示。

经过双极性变换导频序列变为168 b全1数据,用户数据变为由1,-1组成的数据,经过卷积编码成I,Q两路信号,各自经过差分编码后用不同的1 023位I,Q两路Gold码扩频,然后以QPSK方式分别调制余弦和正弦载波,两路数据组合后发射。在接收端,使用相应的信号捕获算法,可以得到信号的Gold码初始相位和一个精度较差的多普勒频偏搜索值,这一步骤的结果是可以解扩信号,但是信号还有(-5,5)kHz的频差,而且这一过程要消耗40个bit的导频符号。也就是说在剩余的128 b导频长度内必须通过相应算法,消除5 kHz频差,完成载波精确同步。

在实际的接收机方案中使用的方法是用I路Gold码,简称Gold_I去分别解扩同相(I路)和正交(Q路)数据,用得到的两路带有频偏的符号数据去调整频偏,而Q路(Gold码,简称Gold_Q不参与频率调整,而是直接解扩Q路数据。当频偏消除后,得到I路和Q路经过差分译码、卷积译码和一系列操作之后就可以得到原始数据。

经过数学模型推导,在码片对齐后,得到用Gold_I分别解扩I路和Q路后得到的用于校正频偏的两路数据为:

式中:C1,C2,φ1,φ2为和采样速率、解扩数据起点位置、扩频码长度有关的常数;△f为经过扫频和信号捕获后的剩余频差,这里△f的取值范围为(-5,5)kHz;Tb=1/Rb为扩频前的符号周期,Rb为符号速率,本系统中Rb=10 Kb/s;p为信号捕获后依次解扩出来的带有频偏的符号数据的次序号。

整个快速载波同步算法流程如下:先进行FFT校频,然后FLL缩小频差,最后PLL精确锁定,分三次分步消除频偏。

1.1 FFT校频

在算法中取I(k+p)的前16个点存储在寄存器中,然后做FFT,那么这16个点相当于在一个已知频率的余弦波上等间隔采样,且采样周期fs=1/Tb=Rb=10 Kb/s,根据FFT理论,在前9个频点中,设得到的频谱能量最大点为第k点,则对应的频率^f=fs/N×(k-1)即为估计频率,其分辨率为10K/16=625 Hz,通过设定变量u5=I(k)Q(k-1)-I(k-1)Q(k)=C3sin(2π△f/10K)(C3为大于0的一个常数),来确定估计出来的频率的正负,当u5<0时,-5 kHz<△f<0;当u5>0时,0<△f<5 kHz。

1.2 FLL(锁频环)

FLL通常采用自动频率跟踪环(AFC)来实现载波频率的跟踪,AFC环的结构如文献中所示。

解扩得到的两路正交信号的点积Dot(k)和叉积Cross(k)分别为:

Dot(k)=I(k-1)I(k)+Q(k-1)Q(k) (3)

Cross(k)=I(k-1)Q(k)-I(k)Q(k-1) (4)

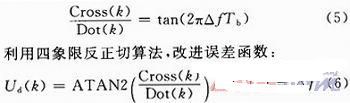

常用的消除符号模糊的CPAFC方法其误差函数为Ud(k)=Cross(k)×sign(Dot(k)),其鉴频特性是非线性的,且鉴频范围为(-Rb/4,Rb/4),将其改进,点积和叉积之间存在如下关系:

这就解决了CPAFC的鉴频非线性问题,且将鉴频范围扩大了一倍至(-Rb/2,Rb/2)。

1.3 PLL(锁相环)

Costas环是一种常用的锁相环,它对载波调制数据不敏感,在无线电接收机中得到了普遍的应用,本方案中采用的Costas环鉴相算法为:

θk=sign(I(k)×Q(k)) (7)

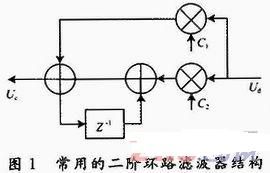

而数字环路滤波器采用二阶环,这是因为如果其直流增益为无穷大而频偏为常数的情况下,二阶环可以实现稳态相位误差和频率误差。其结构如图1所示。

图1中,Ud为输入的鉴频或者鉴相误差函数;C1,C2是环路调整参数,实际应用中需要反复调整至环路性能最佳;Uc为输出的频率或者相位控制字,控制NCO调整频率或者相位。

2 算法仿真结果

系统仿真条件假设为:输入中频信号,符号速率为10 Kb/s,用2路不同的1 023位Gold码扩频,扩频后码片速率为10.23 Mb/s,采样速率为8倍码片速率,经过扫频

- SiGe推出业界最小的GPS和伽利略接收器SE4110S和SE4120S(02-12)

- 卓联时钟产品率先满足最新同步以太网行业标准要求(06-24)

- 一种结构简单UWB接收机的设计与实现(03-23)

- 使用真实数据来测试GPS接收机(06-19)

- 意法半导体Teseo GPS引擎开始批量供货,方便应用于PND和GPS接收机(08-07)

- 宽带数字接收机的信道化设计(02-15)