基于88E6218的SOHO网络开发平台设计

随着互连网的发展,PC用户大量增加,办公SOHO(Small Office,Home Office)化逐渐成为可能。现在市场上已经出现了许多面向SOHO应用的网络通信产品。许多芯片制造厂商纷纷推出了自己的面向SOH0应用的嵌入式网络微处理器芯片。美国Marvell公司生产的88E6218芯片是其中的一种。基于这个芯片,可以搭建一个低成本、高性能的SOH0网络开发平台。通过在上层移植不同软件,可以用于不同的SOHO网络通信产品,如SOHO路由器、SOHO安全网关、SOHO交换机等等。本文介绍88E6218芯片的主要特点,给出基于88E6218的SCHO网络开发平台设计方法。

1 88E6218芯片结构及主要特点

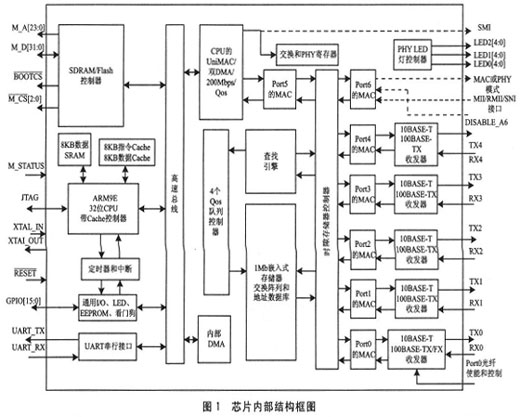

图l为芯片内部的结构框图。

88E6218是美国Marvell公司(宽带通信半导体公司)生产的面向SOHO应用的一款高性价比的嵌入式网络微处理器。该处理器具有以下一些主要特点:

◆芯片内嵌ARM9E的CPU核,采用32位RISC体系,带有DSP指令扩展,最高工作频率可达150 MHz,片内有8 KB指令Cache、8 KB数据Cackc和8 KB数据RAM。

◆芯片集成SDRAM和Flash存储控制器,支持与其他具有存储器地址映射的外设相连接,包括DSP。

◆SDRAM接口可以是16位(最大寻址深度32 MB)或32位(最大寻址深度64 MB)宽度。Flash接口可以是8位、16位或32位,最大寻址深度64 MB。

◆芯片有内部DMA控制器、看门狗定时器、UART串行接口、JTAG调试口以及4个外部片选引脚BOOTCS、M_CSO、M_CS1、M_CS2。

◆芯片带有5个支持IEEE802.3的MAC(Media ACccss Layer,媒体访问层)+PHY(Physical Layer,物理层)接口(Port0~Port4);1个多功能网络接口(Port6)。该接口可配置为RMII(简化媒体独立接口)、MII(媒体独立接口)或SNI(业务接点接口)模式(支持200 Mbps全双工,可直接与交换机或无线局域网互连);1个内部双倍速MII接口(Port5,支持200 Mbps全双工,可直接连接交换端口到CPU内部的MAC)。

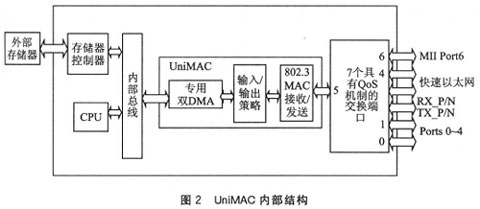

◆芯片提供基于QoS机制的快速以太网交换功能,内部采用拥有专利技术的UniMAC结构,如图2所示,在88E6218内部的CPU与多个快速以太网交换口之间形成高效的网络接口。

◆一款低功耗的CMOS芯片,可提供216条引脚的LQFP封装。

综上所述,88E6218内部功能强,外设接口丰富,可以提供一个单芯片的S0HO路由器/安全网关解决方案。

2 安全平台硬件设计

2.1 平台硬件结构

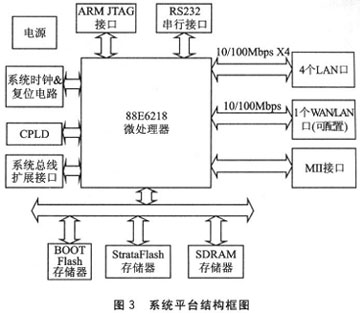

图3是基于88E6218的面向SOHO应用的网络开发平台硬件结构框图。

①电源电路。输入5 V。经过DC-DC变换,分别给擞处理器提供1.5 V、2.5 V和3.3 V的电压。

②系统时钟和复位电路。25 MHz有源晶振经过倍频可为平台提供多种不同的时钟频率;采用专门的微处理器监控芯片为系统提供稳定、可靠的复位信号。

③微处理器,即88E6218,是整个开发平台的工作和控制中心。

④BOOT Flash存储器,用于存放系统的启动程序以及其他在系统掉电后需要保存的数据。

⑤StrataFlash存储器,用于存放嵌入式操作系统和各种用户应用程序。

⑥SDRAM存储器,是平台为操作系统和应用程序提供的运行空间,也是程序运行中大量网络数据的缓存空间。

⑦网络端口。4个10/100 Mhps速率的RJ45接口,为系统提供以太网接入的物理通道;1个WAN接口,可配置为电口或光口,本平台为电口;1个MII接口。

⑧RS232串口,可作为系统的Console调试口或用于平台与其他应用系统的短距离双向串行通信接口。

⑨JTAG接口。通过该接口可对系统进行调试、编程等。

⑩系统总线扩展。引出数据总线、地址总线和必需的控制总线,便于用户根据自身的特定需求,扩展外围电路。

2.2 平台主要硬件单元电路设计

因力88E6218是一个面向SOHO应用的网络微处理器,而且本文设计的开发平台主要用于网络应用,所以下面着重分析较重要的存储器和网络接口电路的工作原理和设计方法。

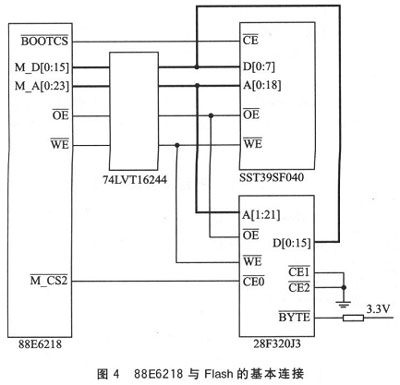

(1)Flash存储器接口电路

Flash存储器具有低功耗、大容量、可整片或分扇区快速烧写、擦除,掉电后信息不丢失等特点,在各种嵌入式系统中得到广泛应用。本系统的Flash存储器包括两部分:一部分是用于存放系统启动程序的Boot Flash,其功能包括对平台硬件的初始化和操作系统的引导等.考虑到启动程序一般容量不大,这里选用了SST39SF040芯片,单片提供8位数据宽度、512 KB存储空间。88E6218提供4个片选引脚,其中BOOTCS专门用于Boot Flash存储器的片选,直接与SST39SF040的CE相连;SST39SF040地址总线A[0:18]与88E6218的地址总线M_A[0:18]相连;8位数据总线D[0:7]与88E6218的低8位数据总线M_D[0:7]相连。另一部分是StrataFlash存储器,用于存放操作系统和各种应用程序,在大多数应用系统中,选用1片16位的Flash存储器芯片(单片容量有1 MB、2 MB、4 MB、8 MB等)构建16位的Flash存储系统已经足够,因此这里选用了Intel的28F320J3芯片,单片提供16位数据宽度、4 MB的存储空间,将88E6218的M_CS2分配用于StrataFlash存储器的片选,直接与28F320J3的CE0相连;88E6218输出使能端OE接28F320J3的OE;写使能端WE接28F320J3的WE;将28F320J3模式选择引脚BYTE上拉,A0悬空,使28F320J3工作在16位数据模式;28F320J3地址总线A[1:21]与88E6218的地址总线M_A[O:20]相连;16位数据总线D[0:15]与88E6218的低16位数据总线M_D[0:15]相连。具体电路连接如图4所示。由于考虑到88E6218的带负载能力,所以把地址、数据总线与部分控制信号线通过一级驱动后再与目标Flash存储器相连。

- VoIP与传统电话网络的弥合期有多久?(11-01)

- ExVPN-让您的网络生活四通八达(01-09)

- NGN之路:十字路口的思考(01-10)

- VoIP在基于MPLS集成模型里面QoS技术 (01-11)

- 光纤通信面临全面升级(01-26)

- 未来5年行业专网NGN 应用高速增长(01-01)