使用FPGA器件最大限度地降低高速DSP密集型系统设计的功耗

DSP密集型系统设计中特别重要。

DSP设计的挑战

DSP密集型系统设计需要复杂的数学计算、高存储器带宽要求,以及具有动态重新配置的 高速串行传输,这些要求在高性能水平下消耗很大的功率。下一代FPGA器件必需能够以尽可能低的功耗来应对这些需求,并且不影响性能。DSP系统设计人员 在设计中使用数个不同的构件(乘法器、存储器、收发器等),而不同系统架构实施方案的功耗有着显着的区别,这取决于使用的FPGA器件。

所有FPGA器件也都使用硬乘法器作为基础计算单元,这个硬乘法器在总体系统功率预算方面举足轻重。为此,美高森美研究了具有不同架构的有限脉冲响应(FIR)滤波器,并且根据乘法器数目对比运作频率,分析了各个器件的功耗。

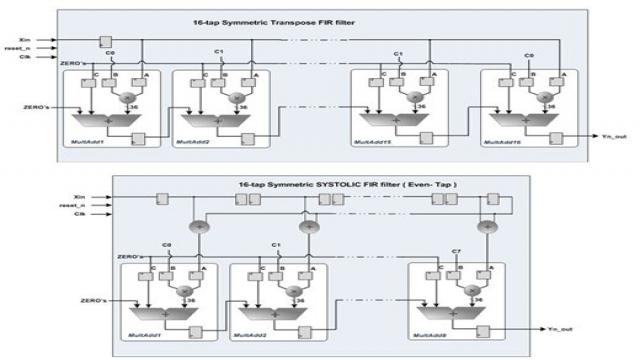

FIR 滤波器经常用于在各种应用中消除不必要噪声,同时提升信号质量,或者修理信号波幅的DSP模块,有着数种FIR滤波器架构,包括转置或收缩(有或没有对称 性) 。这两种架构均具有与总体初始延迟、DSP模块数目、吞吐量或性能,以及管线寄存器数目相关的特性,两种架构之间的区别如图4所示,图中显示16-Tap FIR转置和收缩的对称型款。

图4: 用于对称转置和收缩16-Tap FIR的架构的比较

现 在来总结两种架构之间的区别:转置架构使用管线级并且减少输入扇出以提高运作频率;同时,N-Tap systolic FIR的初始延迟是(2*N -2)周期。比较之下,虽然转置架构的运作频率较低,但其初始延迟较好(N-1周期),而且使用较少的时序资源。这些架构还要考虑其它的因素,最重要的是 滤波器稳定性,尤其是必需考虑大量抽头(tap)数目和加权特性。例如,在需要回声消除的语音处理应用中,在存在大部分回声的近端,权重必需较高,在回声 较少的后续滤波器抽头上较低。

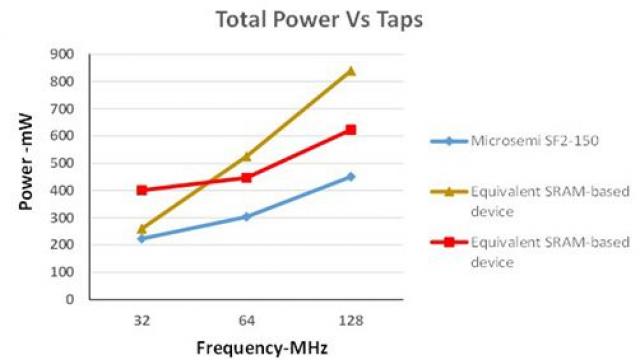

根据使用的架构不同,FPGA的功耗可能显着变化。在一项研究中,使用了功耗预算工具,并且使 用FPGA开发工具套件在32、64和128-Tap Transpose FIR实施方案中测量不同温度下的实际硅器件;研究结果表明FPGA器件通过合适的设计和实施来提供了显着的节能。此外,这些节能在较低的频率和高温下更 加明显。另一个重要发现是,对于最佳性能FPGA器件,功耗与抽头的数目成线性关系。换句话说,如果抽头的数目少,某些性能较差FPGA的功耗数值更差; 对于其它器件,在抽头数目高时,它们的性能更差。这可能与架构问题有关。

图5:来自不同FPGA供应商的32、64、128-Tap FIR总体功耗数值

结论

今 天以DSP为中心的系统设计,面临不断增加的减小功耗的压力。今天基于flash的 FPGA技术不只是减少静态功耗,而是减少总体功耗,正是实现下一代高速DSP密集型系统设计的重要因素,这些设计要求必需在不断缩小的外形尺寸中提供高 算法性能,并具有尽可能低的功耗。

- 单片式降压型稳压器为DSP提供片内电源排序(01-09)

- 什么是PCI总线?其接口芯片的应用(01-26)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)

- 具有多个电压轨的FPGA和DSP电源设计实例(二) (05-22)

- 基于DSP和CPLD的移相全桥软开关电源数字控制器(06-02)