基于8通道并行数据采集PCI模块的设计

数据采集是自动测试系统的主要功能之一,而在一些应用领域,比如超声、医疗电子中,信号的频率范围不同会要求采样率的不同。有时,为了配合信号处理算法,甚至要求采样率在一定范围内随意设定。而且,这些应用通常要求多个通道并行采集,甚至是差分单端方式可选择的输入。针对这些要求,我们提出了一种最多可达12通道的同步并行多通道数据采集方案。该方案能实现的最高采样率为10MS/s,存储深度2×32M×16bit(2个SDRAM),垂直分辨率14bit,可编程增益为1、2、5、10、100五个等级。

设计方案的确定

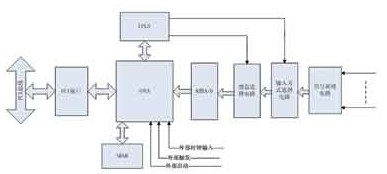

硬件电路主要包括信号调理电路、信号输入方式选择电路、程控增益电路、A/D转换、数据存储、触发控制以及PCI接口几个部分。8个通道输入的模拟信号经信号调理电路调理后,进行单端变差分的转换(前端也可以是直接输入的8路差分信号),由多路开关选择输入方式后,再通过两级可选择增益放大器进行增益控制,最后进入ADC转换成相应的数字信号。而逻辑控制单元在接收到采集命令后,会根据相应的触发方式启动ADC进行采样,再将采样得到的数据通过FPGA内部串并转换逻辑和数据输出仲裁逻辑存储到SDRAM中准备上传。本设计的采集极限指标是8个通道同时同步采集,最大采样速率是单通道10MS/s,连续采样存储时间最大可以达到3.2s。上位机通过32位的数据总线采用查询、中断或者DMA方式将采集的数据读取到内存中进行后期的数据处理和分析。系统的基本结构如图1所示。

图1 系统原理框图

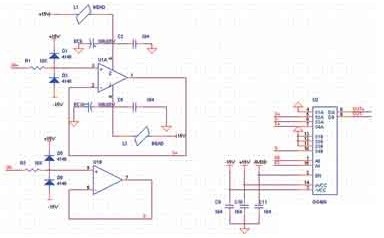

图2 信号输入方式选择电路

信号调理电路设计

在本设计中,信号调理电路包括输入方式选择电路和增益选择电路。此部分中,高输入阻抗、低输出阻抗的普通运算放大器构成的电压跟随器会对前后电路进行隔离,避免后级多路开关的导通阻抗影响前级电路。输入端加两个二极管,提供±15V的钳位电压,形成过压保护。多路开关选择DG409,它是4通道差分多路开关,具有较低的导通阻抗和低功耗和低泄漏电流。信号的输入方式有四种:0输入、单端正极输入、单端负极输入和差分输入,通过DG409正好可以选择这四种输入方式,电路如图2所示。

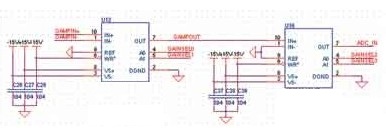

选择一种输入方式后,经过两级可编程增益仪表放大器AD8250,可以实现增益值可选1、2、5、10、100五个等级。AD8250有两个增益控制端A0、A1,写这个两个位,能选择增益值,并通过W/R锁存状态值,从而保证该增益的稳定。本设计通过在FPGA内部设计串行传输逻辑,将数据写入CPLD,然后控制选择信号的输入方式和写AD8250增益控制位。增益选择电路如图3所示。

图3 增益选择电路

数据采集与控制电路设计

A/D转换器是数据采集系统的核心,对A/D器件的选择往往影响到整个系统的性能指标。为了实现8通道并行同步采样可以采用两种方案。一是采用8个独立的A/D转换器,这样不仅成本比较高,而且难以实现8通道同步采样,绘制PCB板的时候也有很大的困难。第二种方式就是本设计的方法,采用一个AD9252来满足最多8个通道的并行同步采样要求。本设计通过NIOSII软核处理器向AD9252发送控制字,以实现8通道并行同步采样。首先,输出14bit的LVDS信号到FPGA,经由串并转换逻辑输出14bit并行数据,再通过仲裁逻辑实现不同通道数据存储位置的不同,最后通过两片SDRAM的乒乓操作实现连续数据采集和传输。

本设计数字控制部分由FPGA和外扩的CPLD共同合作完成。由于设计需要大量的引脚资源,而FPGA的引脚资源有限,所以在FPGA外部通过SPI总线接口外接一片CPLD,从而控制8个通道的输入方式选择和增益选择。FPGA内部嵌入一个NIOSII软核,负责数据采集、数据传输和输入方式以及增益的选择控制。下面详细分析一下这三个数字控制电路的实现方法。

1信号输入方式和增益选择控制逻辑的实现

FPGA和CPLD之间通过串行总线通信。通过在FPGA内部构建一个8bit地址总线,8bit数据线的RAM块,用来存储输入方式和增益选择控制数据。8bit地址线的前三位用来控制通道号,后五位控制所在通道的20种选择状态(4种输入方式,5种增益选择)。8bit数据的前两位是输入方式的选择码,后六位是增益选择码。在FPGA内构建一个地址计数器来进行通道的选择数据提取,该计数器的时钟频率是SPI控制器时钟的32倍。

在CPLD中构建一个48bit的串并转换逻辑,把输入方式选择码和增益选择码送到相应的引脚,从而实现信号输入方式和增益选择控制逻辑的实现。

2数据采集和传输控制逻辑的实现

本设计在FPGA内部设计逻辑如下:

● 读取ADC串行LVDS数据流,然后通过串并转换逻辑把串行数据

- 什么是并行比较型ADC(模数转换器)(01-24)

- 串行及并行A/D转换器在高速数据采集中的采样差别性分析(05-19)

- 应用于并行ADC性能扩展的一种比特滑动流水模数转换方法(09-09)

- 基于打印机并行接口的并行接口(08-03)

- 基于FPGA的高速数字下变频系统设计(10-16)

- 针对Flash存储特性的航天器大容量固态存储技术(10-16)