适用于12 bit流水线ADC采样保持电路的设计

保持电路的核心,它决定了该采样保持电路的精度和建立时间。由于该采样保持电路运用于12 bit 20 MHz流水线ADC,则要求该放大器的输出在25 ns的建立时间内稳定在最终值0.012%。如果将OTA设为单极点放大器,则可估算出OTA的直流增益最好能达到84 dB以上,单位增益带宽必须大于72 MHz。为了能达到较好的性能,一般都留有一定的余量,因此实际上设计中要比这些值大很多。考虑到普通一级运放的增益不够高;两级运放则速度上又达不到,故本文采用增益增强的折叠式共源共栅运放。

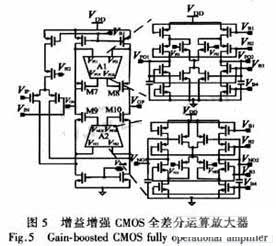

本文采用的放大器为如图5所示的带有A1和A2两个辅助放大器的增益增强型折叠式共源共栅放大器。从工程设计角度考虑,采用统一模块化可简化设计过程,减少设计出错的可能性。因此辅助放大器也采用折叠式共源共栅结构,所有偏置电压都由一个偏置电路产生,并取偏置电流为主运放的1/10,以减小功耗。其中,Al以NMOS管作为输入端,A2以PMOS管作为输入端。考虑到这两个运放的直流输出是为主运放的M7,M8,M9,M10提供直流偏置,不需要大范围的波动,因此采用一种简单实用的共模反馈。另外,辅助放大器的单位增益带宽至少与主放大器的带宽相等,稍大则稳定时间会更短一些,因此可在其输出端接电容来调节带宽,将其控制在主运放第二极点内的合适位置。主运放则采用连续时间型共模反馈。

4 性能仿真和芯片版图

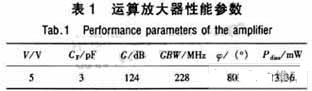

本电路采用CSMC公司的0.5μm CMOS工艺库,应用Spectre对运算放大器和采样保持电路进行仿真验证,表1为典型条件下(TT(工艺角),27℃)运算放大器的性能参数。从表中可以看出,运算放大器的性能满足采样保持电路要求。表中:V为电源电压;CF为负载电容;G为直流增益;GBW为单位增益带宽;?为相位裕度;Pdiss抵为功耗。

在采样保持电路的输入端加差分电压1 V,时钟频率为20 MHz,仿真结果表明输出电压达到LSB/2(0.012%)精度内所需要的时间为14 ns,完全满足12 bit的精度要求。

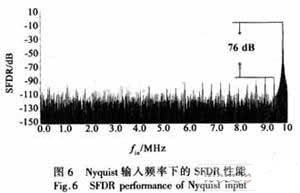

图6是在采样频率为20 MHz下,对由输入信号为Nyquist频率(9.819 3 MHz),Vp-p=2 V的正弦信号,所得到的输出信号频谱图。从图中可以看出电路的SFDR为76 dB,完全满足系统要求。

图7为运算放大器的版图,面积为288μm×128 μm(包括主电路、辅助放大器、偏置和共模反馈电路)。该运算放大器作为一个核心模块已流片测试。测试结果表明该放大器性能与仿真值相近,功能正确,可用于该采样保持电路中。

5 结论

本文设计了一个可用于12 bit,20 MS/s流水线ADC中的采样/保持电路。该电路使用CSMC公司的0.5μm CMOS工艺库,在20 MS/s采样频率下,当输入信号的频率为9.8193 MHz时,SFDR为76 dB,精度达0.012%,完全满足12 bit要求。本文运用增益增强型折叠式运算放大器,以获得较高的增益和带宽。同时采用栅压自举开关,并通过对电路中的开关组合优化,极大的提高了电路的线性性能;采用全差分结构、底极板采样来消除电荷注入和时钟馈通。该采样保持电路能够直接应用于高速高精度模/数转换器等各种高速模拟系统中。(徐星,袁红辉,陈世军,刘强 中国科学院 上海技术物理研究所红外成像材料与器件重点实验室)