新型深亚微米电流灵敏放大器技术设计

随着便携式电子设备(PDA、射频卡、GPS等)的广泛应用,半导体存储器得到了长足的发展。半导体存储器的性能将直接影响到系统在速度等方面的性能。因此,设计能够高速存储的存储器便成为当今集成电路设计的一个研究热点。

存储器的速度主要决定于存储器的读取时间。存储器的读取时间主要是指从地址信号的输入到数据信号的输出所经历的延迟时间,一般由地址输入缓冲器、译码器、存储单元、灵敏放大器、输出缓冲器的延迟时间共同决定。因此,要减少存储器的读取时间,一般有两种途径:一是,减少从地址信号输入到字线选通的延时,由于内部译码器等电路相对固定的形式,用这种方法减少延时是比较有限的;另一种是减少从字线选通到数据输出所经历的延时,这可以通过改进灵敏放大器的设计来实现。可见,高性能灵敏放大器的设计对于存储器性能改进是至关重要的。

灵敏放大器的工作目的是通过放大位线上微小信号的变化而读取存储单元中的数据。一般可以分为电流型灵敏放大器和电压型灵敏放大器两种。由于电流灵敏放大器直接探测输入电流的变化,可以克服电压型灵敏放大器速度较慢、低工作电压下小信号电压增益减少等缺陷,因此电流灵敏放大器受到越来越多的关注。

与一般的灵敏放大器一样,电流灵敏放大器的工作可以分为两个过程:一是,预充电过程,即对位线(BitLine)的寄生电容进行充电,使之恢复到高电平,为下一次读写作准备;二是放大过程,即对位线信号进行放大处理,以读取存储单元所存储的数据。本文就是在这两个过程的基础上,设计出一种新型的电流灵敏放大器。该放大器采用的预充电电路能够在较长时间内(预充电周期以内)保持充电电流处于一个较大值,这样可以减少预充电时间;同时采用两级放大电路对位线信号进行放大,以确保增益、速度达到要求。

1 电流灵敏放大器的基本结构

图1所示为电流灵敏放大器基本结构。其中:Ic是存储单元的电流;Ir是参考电流;REF是输出节点;Ibias是电路偏置电流。Ic由存储单元所存储的信息决定,当存储信息为"1"时,Ic为大电流;当存储信息为"0"时Ic为小电流;Ir的值介于Ic的大、小电流之间。REF节点输出电压为:

式中:rout为输出节点REF处的小信号电阻。当Ic≥Ir时,M2将处于截止区,输出端的电压将上拉到电源电压VDD;Ic≤Ir时,M2将处于线性区,输出端的值将接近于0 V。

2 新型电流灵敏放大器

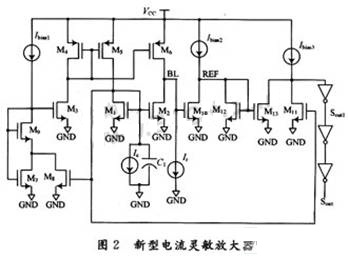

图1所示电流灵敏放大器结构简单,但也存在诸多不足之处,如电源电压不能足够低、预充电电流较小、摆率较低等。对此,文献[7]提出一种自控恒流预充电电路以提高电路读取速度,这一电路的好处在于通过一个反相器实现对预充电电路的关闭,从而确保位线电压不至于太高而影响存储信息。但是通过仿真发现,去掉预充电结构中的反相器后,通过适当调整充电电路晶体管参数,在位线电压不影响存储信息情况下同样能达到较快的读取速度。在此基础上,采用GSMC 0.18 μm工艺设计出一种新型电流灵敏放大器,见图2。在该电路中,M3,M4,M7,M8,M9以及电流源Ibiasl共同构成预充电电路。其中M7,M8,M9和Ibiasl主要用来产生M3的栅极偏压VREF;M3,M4和M5为镜像结构,用来产生预充电电流。Ic和C1的并联结构用模拟存储单元,这种方式能有效地模拟存储单元,同时也提高了仿真效率,其中Ic是读取时存储单元的电流,C1是位线寄生电容。M10,M11,M12,M13和Ibias2,Ibias3构成两级放大器中的第一级,是一个差分放大器。差分放大器的输入信号分别是REF节点和BL节点处的电压。该差分放大器采用一折叠镜像负载,在不增加电源电压情况下可以有效的提高增益。第二级放大器为反相器链。这种反相器链式结构的功能也可以用单个反相器实现,但是采用单个反相器会导致较大的尺寸,从而使寄生电容显著增大从而降低速度。在综合考虑面积、速度等因素之后,这种链式结构更具有优势。

3 电路仿真结果

图2中,当存储单元中存储信息为"1"时,Ic为13 μA;存储单元中存储信息为"0"时,Ic=6 μA。Ir为参考电流,其值介于6 μA和13 μA之间,设定为10.5 μA。设定C1为1 pF,Ibias1=Ibias2=Ibias3=16 μA(见文献[6])。采用上海宏力0.18μm工艺在HSpice下进行仿真。

图3为灵敏放大器在1.8 V电源电压和室温条件下对存储信息"1"放大的仿真图形,其中横坐标是时间,纵坐标是输出节点Sout处的电压。从仿真结果可以看出,在室温(27℃)下读取"1"的响应时间为13 ns(在本文中,所有的仿真都是从0 ns开始启动的),输出电压为电源电压,摆率也比

- 电流灵敏放大器在存储器性能改进中的设计应用(01-30)

- ECL电源开关的应用研究(11-30)

- 电流源电路(01-23)

- 什么是权电流型DAC(数模转换器)(01-24)

- 高速应用中电流反馈运放电路设计分析(01-06)

- 线性光电耦合器在开关电源中的应用(01-15)