一种高增益CMOS全差分运算放大器的设计

由(3)式和(10)式可知,增加输入差分管的W/L、减小负载电容是提高单位增益带宽的有效方法。

3.3 转换速率和建立时间

运算放大器在额定负载及输入阶跃大信号时,输出电压上升段(或下降段)线性部分的斜率 称为转换速率,也叫压摆率。图1 所示运放Vout1-Vout2 的压摆率SR=ID9/CL。本设计中负载电 容CL 为2.6 pF,转换速率要求大于160 V/μs,因此ID9 至少为0.42 mA。

建立时间指当运算放大器构成闭环负反馈时,在限定输出负载并输入阶跃信号的条件下, 输出电压从阶跃信号输入时起至输出电压上升到稳定值的误差容限内所需的时间。它分为线 性建立和非线性建立两个不同的阶段。线性建立阶段指输入差分小信号时,运算放大器的输 出由闭环作用控制的阶段。单位增益带宽越大,线性建立时间越短。非线性建立阶段是指当 输入差分大信号时,运算放大器的输出波形由转换速率决定的阶段,因此可通过适当增加尾 电流来缩短这段时间。

3.4 共模输入范围

输入共模电压范围定义为当差动信号为零时,能维持电路工作在饱和区的共模电平范围。 对于理想差分运算放大器,输入共模电压时输出应为零。而实际的差分运算放大器,电路既 不可能完全对称,尾电流源的输出阻抗也不可能为无穷大。因而,当输入共模电压时输出不 为零;甚至当输入共模电压超出某一范围时,运算放大器就不能再对差模信号进行正常放大。 从图1 可以看到,输入共模电压VIC 有:

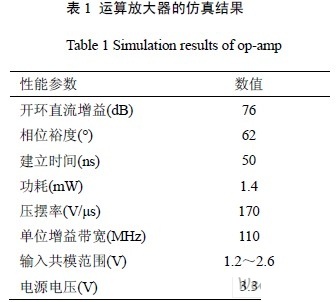

4 仿真结果

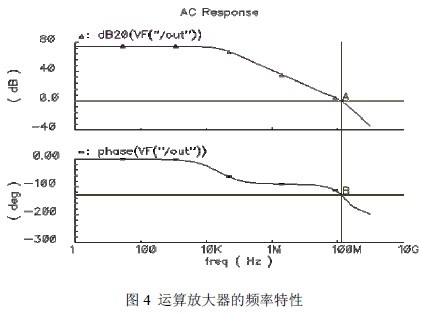

基于 SMIC 0.35 μm CMOS 工艺,在Cadence Spectre 模拟器上对该CMOS 运算放大器进 行仿真。结果如表1 所示。图4 给出了运算放大器的频率响应特性曲线。

5 结论

采用简单的套筒式共源共栅结构,通过分析决定开环直流增益、单位增益带宽、转换速 率和建立时间等主要性能参数的各种因素,实现了一款性能优良的全差分运算放大器。Spectre 仿真表明,运算放大器的各项性能指标均达到设计要求,可应用于高精度音频Σ-Δ A/D 转换 器中。

本文作者创新点:采用结构简单的套筒式共源共栅运算放大器,通过深入分析和优化电 路性能参数,结合Spectre 仿真,从而在保证其它性能的同时,运算放大器获得了高增益、高 单位增益带宽和低功耗。

- 一种增大放大器增益的方法(11-28)

- 改善可编程增益放大器性能的一个技巧(05-21)

- 运用负反馈模型分析实际运算放大器电路(05-07)

- 在数据转换系统中校准增益误差的方法(03-23)

- 一个对温度不敏感的高增益运算放大器设计(09-16)

- 增益天线种类详解(11-12)