改善可编程增益放大器性能的一个技巧

可编程增益放大器(PGA)常用于通信系统,如基站。设计师可以选择目前可用带宽超过500 MHz的全集成单片集成电路PGA,但是要在通信应用中获得很关键的低二阶和三阶失真却不容易。

鉴于上述情况,且考虑到在衰减水平和步长方面要有更多的选择,设计师可能选择采用带有模拟开关和电阻IC的高性能、固定增益放大器来在放大器之前构建一个PGA。作为选择,设计师可根据器件清单订购ASIC。

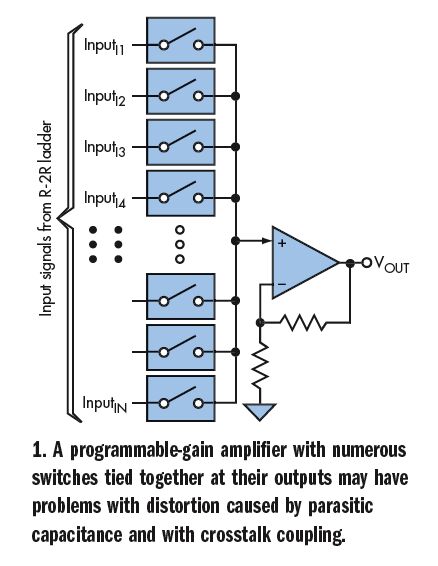

PGA的动态性能主要取决于放大器的特性,放大器的输入阻抗应该高。但是如果开关阵列和布局不是最佳,则PGA的性能会遭破坏。几年前有一个设计思路采用了R-2R梯形,断开每个梯形节点抽头。开关输出接在一起送入放大器。图1为一种类似的结构,本文论述如何改进该电路的性能。

开关数量大增加了开关寄生电容和串扰耦合造成的失真,同时也减少了信号通道的带宽。寄生电容的幅度随信号幅度和工作条件的变化而改变。因此,信号的不同部分以不同的非线性方式传输,这样就引起失真。开关的导通电阻也是非线性的,这会增加失真。MOSFET或双极性开关都可以使用。

|

为减少功耗和热梯度产生的不对称,采用MOS开关(IC或晶体管)可能更好一些。这里讨论的改善PGA性能的技巧可用于任一技术。此外,可以将这些技巧运用到单端或差分结构的PGA中。

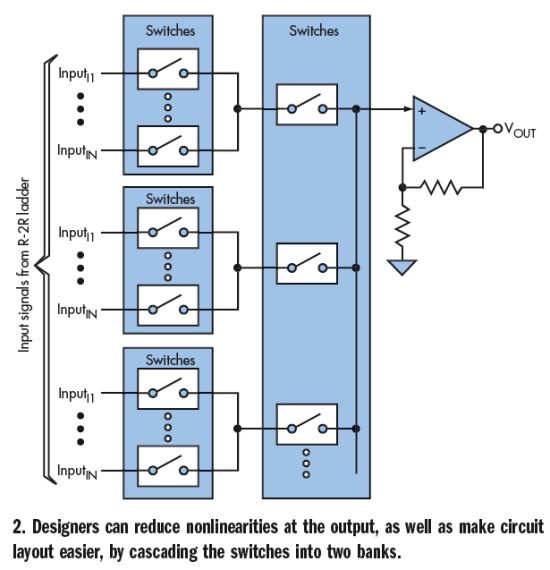

一种减小电容寄生效应和非线性的方法是将开关级联,构成开关数量多的第一排送入开关数少的第二排的结构。这样可以降低输出的非线性,开关在此送入放大器的输入。增加了一个好处,就是使电路布局和走线长度的均衡更容易(见图2)。为了简化译码逻辑使能开关,开关的数量应该以二进制选择为基础进行选择。(图中未示出各开关的逻辑控制)。级联更多的开关排会逐次增加导通电阻,应该避免。

|

如果开关阵列为晶体管级,那么有一个可使失真最小的最佳开关尺寸(即W/L比)。第一排可以是NMOS开关,第二排可以是PMOS开关,这样可获得随电压变化平缓的总体信号路径中的导通电阻。若对速度有要求,这些开关最好都是NMOS。每个开关都应该与其相应的电阻以R-2R梯形结构布放在一起,形成一个单元。

比如,第一排的全部单元以顺时针方向布放。例如,如果是两行,就从下面一行的中心(热中心线)开始输入,顺时针排列。这样,最后一个单元将与第一个输入单元相邻,但两个单元之间有"地"线屏蔽隔离。这种排列可减轻因梯度带来的不对称性。必须特别注意避免不同延迟的输入信号直接耦合到下一排及放大器的节点。

另一个问题是当开关断开时(未被选择的单元接通),其输入端的电压会发生漂移。因此,这些开关的接通会使其在一个未知的电压下启动,产生与输入电压相关的非线性。因此,给开关输入选择提供了一个参考电压,使电压摆幅开始于已知的基线电压(见图3)。

|

作者:Dolly Wu, 高级设计工程师,德州仪器 ,Email: dolly.wu@ti.com

- 削波器漂移补偿可编程增益放大器(01-22)

- ADI实验室电路:如何利用乘法DAC和运算放大器提供可编程增益(02-22)

- 模数接口中的可编程增益放大器(PGA)介绍(07-31)

- 8位高速A/D转换器TLC5510的应用(02-16)

- 改善平板显示器的音频性能(02-13)

- 运算放大器的选择(03-18)