10位逐次逼近型A/D转换器的芯片设计

片的功率消耗和降低匹配精度。如采用单一频率的时钟,则首先要满足较慢的低五位转换时的时间要求,这就会形成高五位在逼近时的"等待"状态,限制了模数转换的速度。

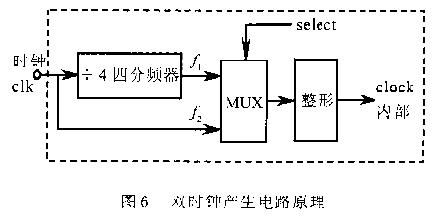

针对上述问题,本文提出了A/D转换器内部工作采用双时钟的设计。通过时序及数字控制逻辑电路,给高五位和低五位的逼近过程分别提供相应的时钟信号,从而减少总体转换时间。如图6所示,外部时钟clk经过四分频,得到一个低频的时钟信号f1以供选择。内部电路在进行逐次逼近转换的时候,产生select信号来选择所需要的时钟信号。所选的时钟信号经过整形电路后送至内部使用。采用双时钟的电路结构,在实现相同的转换精度前提下,转换速率可以有很大的提高。

3 电路的仿真分析及芯片实现

在Cadance的模拟电路仿真环境中,作者使用上华0.6μm 工艺的器件模型对电路性能进行了仿真分析。结果表明,采用双时钟电路结构,可以在不影响转换精度的前提下,提高模数转换器的工作速度。

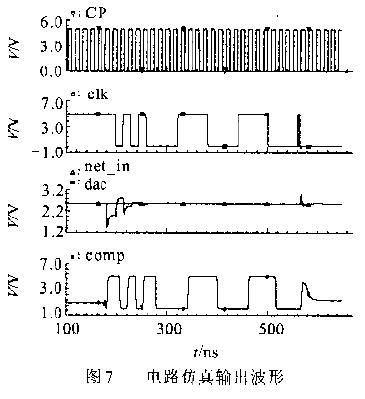

图7是单次模数转换过程的仿真波形。其中,cp是外部电路送入转换器的系统时钟;clk信号是由内部电路产生的变频时钟;net_in信号和dac信号波形反映了转换器的逐次逼近过程;comp信号是比较器的结果输出。图中,comp信号输出的波形代表二进制数字量是1010101010。从图中可以看出,整个转换过程使用到了两种时钟:高五位逼近速度快,相应地选用高频的时钟;低五位逼近速度较慢,选用低频时钟。在双时钟工作时,较好地考虑了高五位和低五位在转换时间上的差异,提高了整个ADC芯片的工作速度。

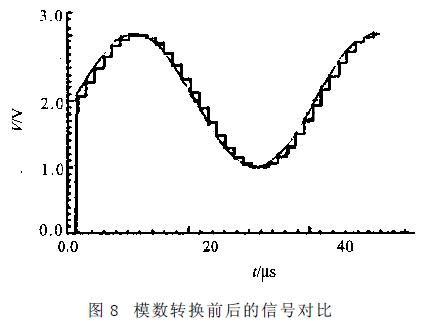

图8是模数转换器的连续工作的仿真波形。其中,Vin是输入到模数转换器的25kHz、振幅1V的正弦波信号,波形dac是模数转换后的数字结果对应的模拟量。考虑到模数转换器的转换需要一定的时间,所以,两个信号的对比是通过信号的平移得到的。从仿真的结果看出,模数转换器工作良好。

在版图设计的时候,考虑到ADC芯片属于数模混合电路,要减小数字电路对模拟电路的干扰,提高整个ADC芯片的抗噪声性能。解决方法是将两种电路尽量远离,以及在敏感的模拟电路周围加上保护环[4]。在模拟电路板图的绘制时,更要仔细考虑元件在电路中的作用,以及元件间的匹配性问题,在走线的时候也要减少信号线之间的串扰。对于元件匹配性要求高的元件,我们采用了共中心的版图画法,尽量减少器件失调。

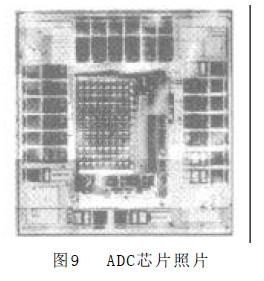

作者设计的10位逐次逼近型ADC在无锡华晶上华0.6μm 、双多晶硅、双金属层CMOS工艺上流片实现。ADC的芯片照片如图9所示。芯片总面积为1.9 mm×1.7mm。其内部核心电路的面积为0.8 mm×1.0mm。

4 结果与结论

流片加工完成后,对实际的模数转换器进行了测试。芯片在单一电源5V下工作,模拟电压输入范围是0~5V。在采样频率为3MHz的条件下工作时,ADC的功率消耗为35mW,其积分非线性(INL)和微分非线性(DNL)均小于0.8LSB。所设计的ADC转换器,已作为嵌入式单元模块用于上海大学微电子中心设计完成的定频空调控制芯片中,并已得到预期的结果。

本文针对内部采用混合式DAC结构的模数转换器,设计了具有变换频率功能的时钟电路结构,为调整和优化此类逐次逼近型ADC提供了一个可参考的方法。该方法较好地处理了比较过程中逼近时间不一致的问题,通过减少高五位逼近时的"等待"时间,提高整体转换的速度。由于逐次逼近型ADC的功耗小、性价比高,在中等精度、中等转换速度的场合具有着良好的应用前景。

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 利用GM6801实现智能快速充电器设计(11-20)

- 利用阻性负载增强LNA稳定性(中)(11-19)

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)