基于PCI总线的GP-IB接口电路设计与实现

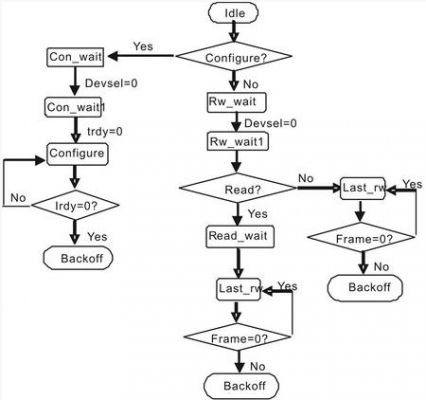

状态机时,不支持CPU的猝发操作。表1给出了状态机的状态名、状态变量和说明,图3给出了状态机的流程图。

图3 状态机设计流程图

下面根据状态机的流程图给出读、写操作时序分析与设计要点:

PCI规范中定义了三种读写操作,即Memory和I/O读写及配置读写。本方案不支持I/O读写,只支持Memory和配置的读写,下面给出Memory映射方式的单周期仿真读写时序。

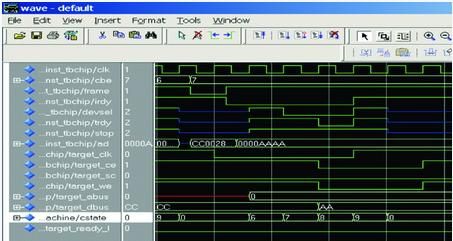

存储器写操作

存储器单周期写操作时序如图4所示,当frame为低电平时启动读写操作,同时给出要写的目标地址ad[31..0]和命令cbe[3..0]=7,cbe等于7表示写寄存器,从设备锁存命令和地址到缓冲区。在第2个clk,主设备将irdy变低,同时给出数据,状态机运行到6,锁存数据给缓冲区,trdy、devsel由高阻变为高电平。在第3个clk,devsel变低,给出主设备应答信号,表示从设备已经响应请求,状态机运行到7。根据写操作,target_we、target_ce变低,并对地址进行译码,放在地址总线上,同时驱动数据总线,表示在对控制芯片进行写操作。在第4个clk,检测到目标设备的target_ready_l为低电平,表示从设备已经做好接受数据的准备,状态机运行到8,将trdy变低。在第5个clk,状态机运行到9,trdy变高,同时主设备将驱动irdy变高,表示一个写周期结束。状态机运行到初始状态,等待下一次操作。target_ce、target_we将延迟变高,结束控制芯片写周期。

图4 存储器写周期时序

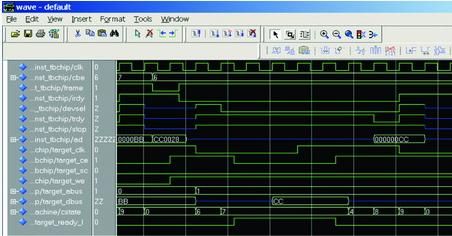

存储器读操作

存储器单周期读操作时序如图5所示,当frame为低电平时启动读写操作,同时给出要写的目标地址ad[31..0]和命令cbe[3..0]=6,从设备锁存该命令和地址。在第2个clk,状态机运行到6,进入读写等待状态,主设备将frame变高,表示单周期模式,trdy、devsel、由高阻变为高电平。在第3个clk,状态机运行到7,并给出应答信号devsel,检测到target_ready_l为高电平,状态机进入等待状态,直到为低电平,然后运行到读等待状态4。在状态机8,trdy变低,从设备将读数据放在ad[31..0]总线上。在状态机9,trdy变高,devsel变高,同时主设备将irdy变高,结束单周期读操作。devsel、trdy回到高阻状态,状态机运行到初始状态,准备下次操作。

图5 存储器读周期时序

结语

本设计占用芯片的资源少,可移植性强,根据设备不同的需求可以进行设计更改,在很多测试仪器中都得到了广泛的应用。

参考文献:

1.李贵山、陈金鹏,PCI局部总线及其应用,西安电子科技大学出版社,2003

2. 候伯亨、顾新,VHDL硬件描述语言与电路设计,西安电子科技大学出版社,1997

- PCI总线数据输出板驱动程序的开发(05-16)

- PCI9030及其PCI总线接口电路设计(07-28)

- 基于PCI总线的雷达视频高速数据采集接口设计(10-16)

- 基于CPCI总线的智能A/D,D/A模块设计(01-28)

- 基于PCI总线的数字图像处理仿真系统设计方案(01-21)

- PCI总线和PCIE总线的差异(12-04)