基于PCI总线的GP-IB接口电路设计与实现

前言

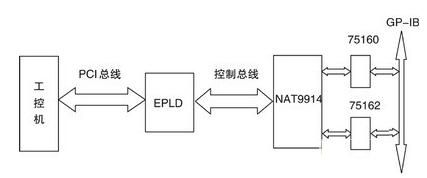

基于PCI总线的GP-IB接口电路框图如图1所示,工控机采用PCI-104堆栈结构,通过PCI总线和EPLD相连,数据总线为32bit,传输速率为33MHz。EPLD完成PCI总线接口电路的设计和NAT9914接口芯片的控制,通过驱动芯片75160和75162完成GP-IB的接口通信。在此重点介绍EPLD内部电路设计。

图1 GP-IB接口电路结构框图

EPLD内部电路设计

PCI局部总线很复杂,PCI局部总线也在不断的发展中,现在已经衍生有CPCI、PCI EXPRESS等总线标准。PCI局部总线定义的功能很强大,当然如果需要将所有的PCI局部总线的要求都能实现,购买PCI局部总线的专用集成电路或IP核是最佳选择,因为PCI局部总线的硬件设计过于庞大,全部实现有一定的难度。如果设备只是作为从设备,根据设计要求实现起来也不是很复杂,很多功能如仲裁、边界扫描及错误报告等功能就可以不用实现,甚至像奇偶校验、重试、突发传输等功能也可以不用实现。

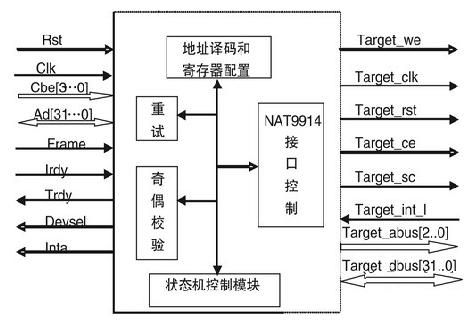

根据GP-IB接口卡的功能,本文主要介绍在EPLD中实现PCI总线接口电路的设计,并且能够正确操作GP-IB总线协议的控制芯片NAT9914。EPLD的容量较小,我们采用XILINX公司的XC95288XL器件,只有288个宏单元,经过设计优化,最终成功装载。其实现原理框图如图2所示。

图2 EPLD内部电路框图

PCI接口信号设计

设计PCI接口信号很关键,PCI总线规范定义的信号很多,在设计过程中必须有所取舍。下面按照PCI总线规范的要求,根据设计电路的实际需求,设计如下接口信号:

Rst : 上电复位信号,低电平有效。

Clk : 时钟信号33MHz。

Cbe[3..0] : 命令、字节使能信号。

Ad[31..0] : 地址、数据多路复用的三态输入/输出信号。

Frame : 帧周期信号,由主设备驱动,表示当前主设备一次交易的开始和持续时间。

Irdy : 主设备准备好信号。

Trdy : 从设备数据准备好信号。

Devsel : 从设备被选中响应信号。

Inta :从设备中断请求,低有效。

在设计时舍弃的信号有:Par、Stop、Perr、Serr、Req、Gnt。

GP-IB接口芯片控制信号设计

根据电路要求,设计如下接口信号,用来完成对NAT9914和驱动芯片的控制,实现PCI到GP-IB接口的转换。

Target_clk: GP-IB接口控制芯片时钟,本方案设计为33MHz时钟的8分频。

Target_rst:复位脉冲信号,低电平复位。

Target_ce: 读写使能,高电平为读,低电平为写。

Target_sc:标识GP-IB接口卡作为控者,还是作为普通器件。

Target_we:写使能控制,低电平有效。

Target_int_l:控制芯片中断输出,低电平有效。

Target_abus:有效地址输出。

Target_dbus:三态数据输入/输出总线。

电路优化设计

图2给出了PCI总线接口电路的原理框图,由于EPLD容量较小,在设计时必须尽量减少不必要的电路设计,并对电路设计进行优化,下面给出各电路模块的功能设计:

译码电路

PCI总线命令编码方式有12种,在本设计中我们只实现配置读、配置写、存储器读和存储器写四种编码交易类型。译码功能电路工作在地址周期,包括命令译码、地址译码和命令/地址锁存等三项功能。在Frame变低的第一个时钟周期内,译码电路对来自主设备的命令Cbe[3..0]进行译码,并向状态机控制模块发出是配置读写还是存储器读写命令,同时锁存地址。

配置寄存器

在PCI规范中,配置空间是一个容量为256字节并具有特定记录结构或模型的地址空间,该空间又分为头标区和设备有关区两部分。在配置寄存器中不用的寄存器当CPU读的时候,将默认为零。

重试

GP-IB控制芯片寄存器响应完全能够满足PCI规范的要求,不需要进行重试,这部分功能不再实现。

奇偶校验

在BIOS中可以对奇偶校验进行屏蔽和开放,为了减少设计的复杂性,奇偶校验功能在EPLD中没有实现,在BIOS中进行了屏蔽。

NAT9914接口控制电路

NAT9914接口控制电路主要完成内部总线到外设的时序控制。GP-IB总线接口采用的是负逻辑电平设计,考虑到EPLD的容量有限,在设计时数据传输不支持DMA模式,只支持单周期CPU读写。由于CPU读数据时延迟较大,在对PCI状态机设计时必须进行读延迟等待。

状态机的设计与实现

状态机的设计是整个设计中的核心部分,它主要用来控制从设备和PCI总线的时序。在本设计方案中,配置过程的完成和存储器的读写都是由状态机来完成的。由于EPLD的容量有限,GP-IB接口芯片的读写速度比较慢,在设计

- PCI总线数据输出板驱动程序的开发(05-16)

- PCI9030及其PCI总线接口电路设计(07-28)

- 基于PCI总线的雷达视频高速数据采集接口设计(10-16)

- 基于CPCI总线的智能A/D,D/A模块设计(01-28)

- 基于PCI总线的数字图像处理仿真系统设计方案(01-21)

- PCI总线和PCIE总线的差异(12-04)