一种恒跨导CMOS运算放大器的设计

引言

随着微电子技术的发展,混合信号集成电路得到了广泛应用。集成电路已发展到系统级芯片(SOC)阶段。特别是随着CMOS工艺的进步,CMOS电路所具有的低成本、低功耗以及高速度等特点,使集成电路的应用、理论和技术发生了深刻的变化。另外随着CMOS模拟电路设计的不断进步,CMOS技术不仅是实现SOC的最好选择,而且是实现模拟集成电路的有效方法。近年来,基于CMOS技术的低压、低功耗便携式产品在人们日常生活中的应用越来越广泛。在低电源电压条件下,需要增大运放输入/输出信号的动态范围,实现轨对轨输出,即供电电源电压和地(或另一电源电压)之间的输入共模范围和输出摆幅。对于轨对轨运放,输入级中跨导会发生变化,这将会引起信号的失真、环路增益的变化等。所以,必须使输入级跨导在整个共模输入范围内保持恒定。

本设计是采用电流镜改变互补差分对尾电流来获取恒定跨导以实现轨对轨。为了获得较大的带宽和增益,输入级中采用了电流源控制,中间级的电流求和电路采用折叠式共源共栅电路,输出级采用AB类控制电路,并且通过适当选择最佳的管长比,减少了补偿的复杂度。

1 输入级原理与设计

轨对轨运算放大器在整个共模范围内,输入级的跨导基本保持恒定,这对低电压应用是至关重要的,其在低电源电压和单电源电压下可以有宽的输入共模电压范围和输出摆幅。轨对轨输入/输出功能扩大了动态范围,最大限度地提高了放大器的整体性能。

1.1 基本原理

一般情况下,运放的输入级都采用差分放大器,通过NMOS或PMOS的差分对可实现基本的差分输入。然而这种单一的差分,并不能满足轨对轨输入的需求。

本文设计的输入电路如图1所示,输入电路由一个PMOS输入对和一个NMOS输入对并连构成。工作原理如下:

(1)若Vss≤Vcm≤VgsP+Vdsat,仅PMOS输入对导通。其中,Vcm为共模输入电压,Vss为负电源,VgsP为PMOS管的栅源电压,Vdsat为电流源两端的电压。

(2)若Vdd≤Vcm≤VgsN+VDSAT,仅NMOS输入对导通。其中,Vdd为正电源,VgsN为NMOS管的栅源电压。

(3)若Vcm处于以上两种情况之外,PMOS,NMOS输入对均导通。

由此可见,NMOS与PMOS差分对并连时,Vss≤Vcm≤Vdd。

对于该输入级电路的跨导具体分析如下:

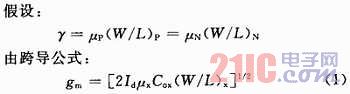

可知:若PMOS或NMOS输入对分别单独导通,其跨导均为:

式中:μP,μN分别为PMOS,NMOS载流子迁移率,Cox为单位面积的栅氧化层电容。所以,当Vcm处于输入差分对管不同的工作状态时,跨导不恒定,即两个MOS差分对管同时导通是二者分别单独工作时的2倍。

1.2 输入级的设计

非恒定跨导是轨对轨运放中存在的主要问题之一,实现恒跨导的方法有多种。其中电平移位法需要及时调整,具有电路不稳定的缺点。齐纳二极管恒压法可以节约芯片面积,降低功耗,但对跨导控制不是很理想。最大电流选择法的电路设计比较复杂。本文采用电流镜改变互补差分对管的尾电流来实现恒跨导。

通过电流镜改变互补差分对管的尾电流来使跨导恒定。基于式(2),式(3),可采用3倍电流镜和电流开关使2个差分对管单独工作时的电流为原来单独导通时的4倍,这样整个输入级的跨导就可以保持恒定。通过给开关管加固定偏压来控制输入差分对管尾电流的变化,进行偏压选取,使尾电流的变化和输入电压同步变化。

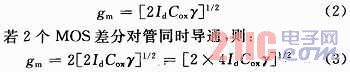

运算放大器整个电路组成如图2所示,在输入级中,PMOS差分对M1,M2和NMOS差分对M3,M4组成互补差分对,2个开关管M5,M8分别控制3倍电流镜M6,M7和M9,M10产生4倍尾电流,控制电路的输入差分对管尾电流。MOS管M51,M52,M53以及电压源VB1,VB2,电流源IB1组成偏置电路,给M5提供所需电压。当Vcm接近于Vss时,M1,M2,M3导通,M5截止,则尾电流经开关管M8和3倍电流镜M9,M10给PMOS差分对提供4倍尾电流;当Vcm接近于Vdd时,M3,M4,M5导通,M8截止,则尾电流经开关管M5和3倍电流镜M6,M7给PMOS差分对提供4倍尾电流;当Vcm处于中间状态时,开关管M5,M8均截止,此时仅MOS管MA,MB作为电流源提供尾电流。从而,可以得到恒定的跨导。

2 输出级

2.1 AB类输出级

运算放大器的输出级可在允许失真范围内将功率传输给负载,对高性能运放来讲,要求输出级可以向负载传输正、负双向电流,提供尽可能大的输出电压摆幅,同时要求拥有高的效率、小的失真及良好的频率特性。因此,为了最大效率地利用电源,输出级必须具有大的输出摆幅和尽可能小的静态电流。为此可采用AB类的输出级。

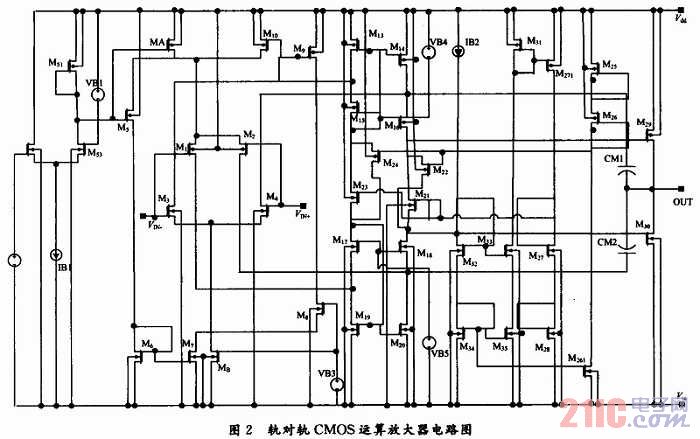

AB类输出级结合了A类和B类优点,在静态功耗及输出电流方面做出了折衷,大大减小了交越失真,同时实现了较大的输出电流。为了减少芯片面积,可将AB类驱动电路放入折叠共源共栅求和电路中去,由于浮动AB类控制器可以产生有别于供电电压的静态电流,在输出级中采用叠接二极管电路,可以对AB类控制器产生栅压偏置。如图2所示。浮动电流源M21,M22对于折叠共源共栅电流求和电路和AB类控制器产生偏置,其与图3所示的AB类驱动电路中M19,M20有着相同的结构,这样,输出管M27,M28的静态电流不会受到输入共模电压的影响。

由于MOS晶体管的栅源电压的限制,为了获得轨对轨的输出范围,在输出级使用共源级的晶体管是必须的。图3所示的为该运算放大器的AB类输出级,M21,M22,IB5和M28,M24,IB8分别提供晶体管M20,M19的栅极偏置电压。M25,M26的静态电流分别由M21,M22,M20,IB7,IB6,IB5和M23,M24,M19,IB7,IB6,IB8确定;输出级工作时M25,M26的栅极电压差是稳定的,并以此来保证该输出级为AB类输出级。该输出级的缺点是输出管M25,M26的静态电流会受到输入共模电压的影响。图2中采用MOS管M31~M35,M26,M27组成的偏置电路来提供电路所需电流。

2.2 频率补偿

两级CMOS运算放大器的密勒补偿有直接密勒补偿和共源共栅密勒补偿方法。用共源共栅密勒补偿技术设计出的CMOS运放与直接密勒补偿相比,具有更大的单位增益带宽、更大的摆率和更小的信号建立时间等优点,还可以在达到相同补偿效果的情况下极大地减小版图尺寸。

对于该运放的频率补偿,采用了共源共栅密勒补偿方式。如图2所示,总体设计的补偿回路中包含了共源共栅级M14,M16。

本文采用0.5 pF的密勒补偿电容,通过仿真可得到相位裕度为70°,单位增益带宽为121 MHz,补偿效果较好。

- 高增益低功耗CMOS运算跨导放大器的设计(02-20)

- 一种用于高速ADC的采样保持电源电路的设计(10-21)

- 一种改进的增益增强共源共栅放大器的设计(07-12)

- 基于衬底驱动技术的模拟电路设计(05-18)

- 基于跨导放大器的电流模式积分单元的设计(07-03)

- 跨导放大器实现电流模式积分单元(02-14)