基于超薄外延技术的双扩散新型D-RESURF LDMOS设计

引言

SPIC(Smart Power IC)目前已经被广泛应用于开关电源、电机驱动、工业控制、汽车电子、日常照明、家用电器等领域。在SPIC中,通常需要将耐高压的功率器件与低压控制电路集成在同一芯片上。在高压功率器件应用领域中,LDMOS由于工作电流密度大、导通电阻低、开关特性好等优点而被广泛采用。从工艺应用角度看,LDMOS拥有横向结构的优势,可采用BCD工艺条件将LDMOS、CMOS和BJT器件单片集成在同一硅片上。在LDMOS设计过程中,新技术的应用决定了器件的耐压和导通电阻特性。在本文中,LDMOS成熟地在结构中引入了D-RESURF技术,D-RESURF技术是在N型漂移区表面引入P型降场层形成节终端扩展区,可使表面电场得到改善,同时增加了器件反向击穿电压;另外D-RESURF技术也使漂移区单位面积可注入杂质密度增大,从而降低了器件的导通电阻。

目前,高耐压的LDMOS一般采用厚度为10μm左右的外延层,其外延厚度远高于目前标准CMOS工艺,并且用于高压集成时需要增加对通隔离的时间,因而不易与标准CMOS工艺兼容。为了解决上述问题,本文采用了P埋层的薄外延完善该LDMOS结构,以传统CMOS工艺,在厚度为4.5μm的超薄外延层上,仿真设计了耐压为700V以上的LDMOS器件。

1 器件结构与分析

本文中所采用的双扩散高功率的BCD工艺涉及了多种类型器件,主要包括耐压为700V的高压LDMOS、耐压为40V的中压MOS管、5.8V低压CMOS器件、二极管、电阻等。因此在设计LDMOS的过程中需要考虑与其他器件在工艺加工过程、注入浓度、版次等方面的匹配性。

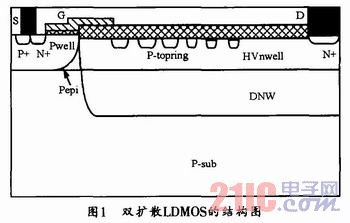

新型双扩散LDMOS的设计要求是:在4.5μm超薄外延层工艺条件下,可以满足700V以上高耐压要求,同时尽可能的降低导通电阻;在此基础上压缩漂移区长度,优化器件的结构尺寸,达到减小芯片版图面积和制造成本的目的。双扩散LDMOS的结构如图1所示,多环P型降场层P-topring被分为数个隔离的岛,用以改善器件的表面电场;图中的P-sub表示工艺中采用P型衬底材料;LDMOS的耐压漂移区分为上下两部分:

HVnwel表示N型外延层漂移区部分,DNW表示器件衬底漂移区部分;Pwell表示LDMOS的体区,用来形成MOS器件的沟道。LDMOS的栅板位于体区上方,它的右侧延伸了一段到场氧上,形成场板,用来改善器件表面电场分布。

1.1 器件表面降场层的结构描述

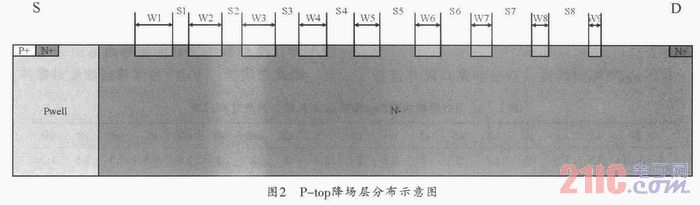

在器件表面降场层的设计中采用了DRESURF技术,在器件的源漏端之间的N型漂移区表面引入了相反导电类型的多个P-top环形掺杂区。这些环形降场层的设计是基于横向变掺杂(VLD)技术,VLD技术是通过改变杂质注入窗口的尺寸和间距,有效地控制P-top降场层在器件表面的浓度分布。在P型杂质以相同的注入浓度注入后,杂质通过不同间距和尺寸的窗口进入漂移区表面,在相同的环境温度下产生横向和纵向扩散,最终在器件表面的降场层浓度分布近似线性,从漏端到源端浓度的线性增加,可以使表面电场的分布均匀。P-top降场层被分为九个不同间隔的区域,如图2所示,P-top从左到右各环的横向尺寸Wn在逐渐变大,而环间距Sn则逐渐变小,实现从左到右(从漏到源)P-top降场层浓度的近似线性分布。

在这些P-top区域的P型杂质是以高能量,高浓度的方式注入,这样可以确保器件HNV漂移区保持较高的杂质浓度来耗尽P-top反型区,在漂移区外延层内,如此高的积分电荷器件确保了器件拥有较低的导通电阻。

在用MEDICI、Tsuprem4软件对该器件进行工艺器件联合仿真时,观察结果如LDMOS表面电场分布图中所示,漂移区内由高浓度P-top环引起的电场波峰均匀地分布在漂移区电场中部,各电场波峰值大小相似,约为2×1015V/cm。在该分布状况下,器件源漏间漂移区的表面电场的耐压分布得到有效地改善。

1.2 器件漂移区的结构分布

N型漂移区的浓度分布和尺寸结构,决定着LDMOS电场分布和比导通电阻的大小。为实现与中、低压MOS良好的工艺兼容,器件漂移区的形成采用了双阱双次注入的设计方法,通过对外延层和衬底表面分别注入不同剂量N型杂质来实现。在外延生长前,在衬底表面注入P型材料形成漂移区的DNW部分;生长4.5μm薄外延后,在DNW正上方的超薄外延中实现第二次注入扩散,完成漂移区的HNV部分。双注入不但成功地在4.5μm超薄外延的基础上使漂移区结深达到10μm,同时由于漂移区的截面积大幅增加,也可以在横向上大幅缩短了漂移区长度。

在仿真设计过程中,由于P-top降场层的大剂量注入,允许漂移区的HNV区域保持较高的浓度分布,器件比导通电阻随之降低。由于DNW杂质在外延生长加热过程中会向上反扩,增大外延层的浓度,所以DNW区域的注入浓度要小于HNV。为防止过早发生体内击穿,DNW在外延生长前需要较长时间的高温加热,使得注入结深向衬底扩散,确保器件在衬底纵向保持6μm漂移区结深。两次不同剂量,不同加热环境的注入,实现了器件电场分布的优化设计,有效地满足了器件在不同区域的技术需求。

高压节能 LDMOS D-RESURF结构 相关文章:

- 用于军事和航空航天领域的高可靠性技术(06-24)

- 电平位移电路应用于负电源的设计(08-24)

- 检测LDMOS漏端电压判断是否过流方案(08-29)

- 最新耐用型大功率LDMOS晶体管耐用测试及应用类型(06-04)