基于超薄外延技术的双扩散新型D-RESURF LDMOS设计

2 器件的仿真优化设计

设计中应用MEDICI、Tsuprem4软件对器件进行优化。在符合4.5μm薄外延的工艺条件下,为改善器件表面电场,使器件最高耐压大于700V的设计要求,对P-top注入剂量与结构尺寸进行了仿真优化设计。同时,分析了漂移区浓度对击穿电压和导通电阻的影响,通过仿真得出最佳浓度分布范围。

2.1 P-top注入剂量与结构尺寸的仿真优化

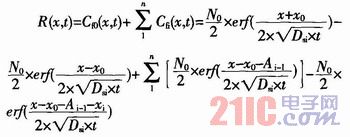

由于在纵向P-top降场层的结深都很浅,所以其浓度变化可以忽略不计。在这里主要分析P-top降场层沿x方向的一维模型,多环注入时杂质浓度分布为R(x,t),Cfo(x,t)和Cfi(x,t)分别是当推结时间(T)后的第一个环和第i个环的杂质浓度分布,其公式为:

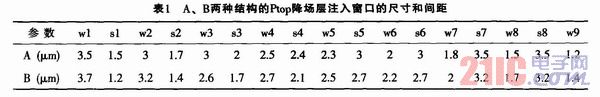

通过公式可以调节在版图中P-top环的窗口尺寸和间距的大小,实现P-top降场层的线性变掺杂。考虑工艺制作水平和误差等因素,为避免出现工艺失真,窗口的尺寸和间距不易太小,但如果窗口的间距太大,就不易实现降场层的线性变掺杂,因此需选取合适的窗口尺寸和间距。经过仿真设计与实际测试,得到两组具体的窗口尺寸,见表1。

对P-top降场层的注入剂量和窗口尺寸进行优化设计,其模拟结果如图4所示,由图可见窗口尺寸较小时(A结构)更近似为线性变掺杂,其浓度在2.2E13cm-3~3E13cm-3范围内都满足器件击穿电压大于700V,而窗口尺寸较大的B结构注入剂量只在2.3E13cm-3~2.8E13cm-3范围内才满足器件击穿电压大于700V,显然其变化范围较小,提高了工艺的复杂程度,所以这里选取A结构中最优值2.5E13cm-3进行工艺设计。

2.2 漂移区浓度对击穿电压和导通电阻的影晌

当漏端电位从零开始增加到220V左右时,体内PN节耗尽区随着电压的增加而扩展,直到整个漂移区完全耗尽(此时体内PN节的峰值电场远远小于击穿电场的最小值),电压继续增大过程中,器件表面的P-top、N-结与器件体内的N-、P-sub结的电场峰值在随之上升,在N型漂移区总的注入剂量不变的情况下,HNV注入剂量的增加会使LDMOS表面电场的击穿点的由漏端向P-top的源端方向转移。表现为HNV注入剂量为1.1E 12cm-2~1.35E12cm-2时,N型漂移区浓度偏低,LDMOS的漂移区会在较低的漏源电压下全部耗尽,电场在漏区集中,导致器件首先在漏区/N型漂移区处击穿;N型漂移区表面杂质浓度的增加会使P-top完全耗尽的同时、表面电场的分布更加均匀,导通电阻趋于下降。当HNV注入继续上升时,N型漂移区浓度偏高时,LDMOS的漂移区无法完全耗尽,电场在P-top降场层靠源区一侧集中,器件同样会过早击穿。于此同时DNW的注入浓度在逐步下降,使得整体漂移区比导通电阻会逐渐增加。因此必须折中考虑N型漂移区浓度对器件击穿电压和比导通电阻的影响。

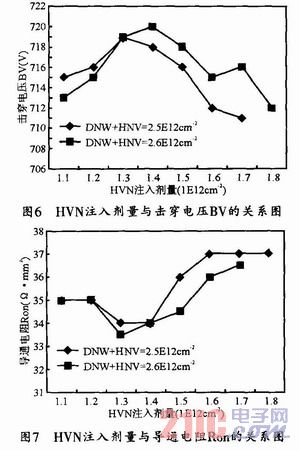

TSUPREM4和MEDICI模拟仿真漂移区浓度分布,当漂移区总注入剂量在2.4E12cm-2~2.7E12cm-2范围内,HNV保持注入剂量在1.1E12cm-2~1.8E12cm-2变化时,器件击穿电压大于700V。考虑到工艺误差等因素,选取漂移区总注入剂量分别为2.5E12cm-2和2.6E12cm-2,HNV注入剂量由1.1E12cm-2~1.8E12cm-2变化时,观察分析击穿电压BV与导通电阻Ron变化情况如图6、7所示。

观察HVN注入剂量与击穿电压BV和导通电阻Ron的关系图,当HNV注入剂量由1.1E12cm-2增加时,器件表面浓度得到改善,使击穿电压上升,同时导通电阻也在相应减小,随着浓度的增加,器件漂移区浓度分布趋于最优化。当HNV注入剂量超过1.5E12cm-2继续增加时,漂移区表面浓度过剩,器件此时击穿发生降场层附近。表现为击穿电压逐渐降低,与此同时,漂移区DNW的注入随着HNV的增加而逐渐降低,器件漂移区上下浓度分布失衡,导致器件的导通电阻增大。因此,流片时选取HNV注入剂量为1.3E12cm-2~1.5E12cm-2时,DNW注入剂量为1.1E12 cm-2~1.3E12cm-2。此时对应仿真结果导通电阻小于35Ω·cm2,击穿电压BV大于714V。

3 结束语

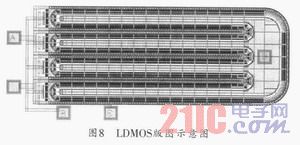

本文对一种基于超薄外延技术的双阱LDMOS进行设计研究,该新型器件采用了D-RESURF,横向变掺杂(VLD),双阱注入漂移区等技术。通过对漂移区表面降场层的几何尺寸和注入浓度的仿真优化,改善了器件表面电场的耐压特性,同时在漂移区总注入剂量不变的情况下,研究了HNV注入浓度与击穿电压与导通电阻的关系,分析研究仿真结果,得出最佳浓度分布。根据这些仿真设计结果,对该型LDMOS进行投片验证,其器件版图如图8所示。当P-top注入剂量为2.5E13cm-3,HNV注入剂量为1.3E12cm-2。DNW注入剂量为1.3E12cm-2时,测试器件结果表明LDMOS击穿电压可以达到690V,结果接近设计要求,实现了与中、低压器件的良好工艺兼容。

高压节能 LDMOS D-RESURF结构 相关文章:

- 用于军事和航空航天领域的高可靠性技术(06-24)

- 电平位移电路应用于负电源的设计(08-24)

- 检测LDMOS漏端电压判断是否过流方案(08-29)

- 最新耐用型大功率LDMOS晶体管耐用测试及应用类型(06-04)