|

电路原理分析

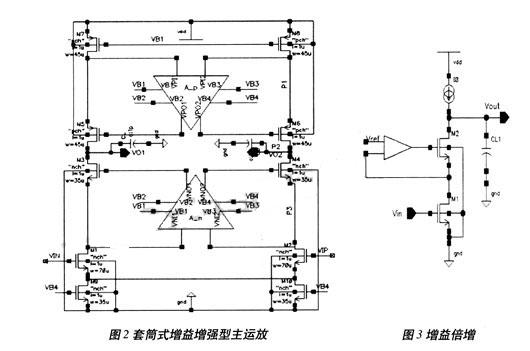

增益倍增

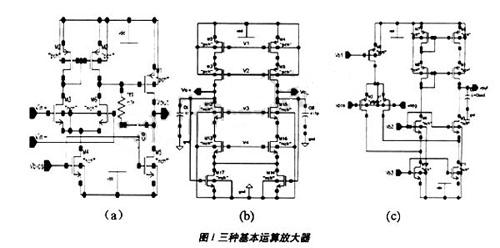

为了提高增益,在共源共栅结构上附加辅助运算放大器,如图3所示,可以增强共源共栅效应。辅助运放的放大倍数为Aadd,通过减小由输出到输入管漏极的反馈,输出可增大Aadd。倍,也即等效于:Rout≈(gm2rds2(Aadd+1)+1)rdsl+rds2。其中,g m2是M2管跨导,rds1与rds2:分别为Ml与M2的输出阻抗。因此电路的直流增益也会增大同样的倍数,Av=gm1Rout≈-gm1rds2 (gm2rds2((Aadd+1)+1)。

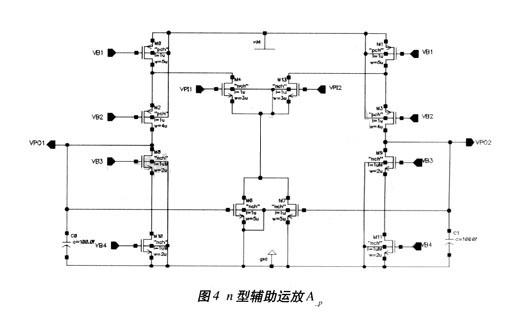

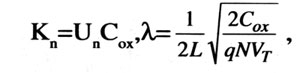

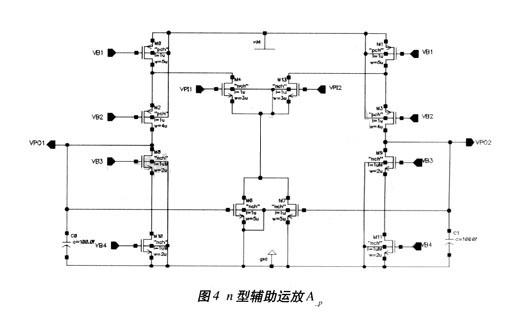

同理,给图2中的套筒式主运放加上辅助运放后,其直流增益可提高为Av=-gm1[(gm5rds5 rds7 (Aadd_p)// (gm3rds3 (rds9// rds1) Aadd_n)分别是辅助运放Aadd_n和Aadd_p。的放大倍数。图4中示了n型辅助运放A_p的结构。

p型辅助放A_n用于推进主运放的M 3、M4管,n型辅助运放A_p.用于推 进主运放的M5、M6管。辅助运放采用折叠式结构,不需要太快的速度和建立时间,因此其尾电流取为主运放的l/10,大大降低了整个电路的功耗和面积。 频率响应分析

图2中全差分套筒式共源共栅运放的主极点在P.点,频率为Wpl=-l/RoutCL;次极点位于P2或P3点。通常由于p管的迁移率比n管的迁移率小,因此p管的过驱动电压较大,导致宽长比W/L。也较大,即P2点的电容比P3的电容大。因此可以认为P2点为次主极点,wP2=-gm5/cp,其中gm5为M5管的跨导,Cp主要包括M5管的栅源电容c。。和M3管的栅漏电容Ggd。而主运放的单位增益频率为WU=gm1/CL。,其中gm1为M1管的跨导。当加入辅助运放时,附加的增益部分与M5管形成闭环,若附加增益部分速度太快,电路就可能变得不稳定。又因为辅助运放增加了一对零极点Wdoiblet,如果设计不好,就会严重影响运放的建立特性。因此应使这对零极点尽量靠近,并且尽量远离主运放的单位增益频率,同时还要小于主运放的次主极点,即:βWU Wdoublet WP,其中β是闭环反馈系数。

|

主运放和辅助运放的设计方法

在设计套筒式共源共栅主运放时,首先根据最大输出摆幅的要求,分配过驱动电压Vod并设置静态工作点。由图可得:Vout.max=Vdd一(|Vod7|+|Vod5 |),Vout.min=Wod9+Voal+Vod3,设输出摆幅为1.5V,则|Vod7|+|Vod5 |+Vod9+V0d1+Vod3=3.3-1.5=1.8V,由于p管M7、M5的迁移率低,给它们均分配0.45V的过驱动电压,剩余的平均分配给M9、M1、M3各0.3V。再由阀值电压公式Vgs=Vt+Vod知:允许的最小输入共模电平等于Vgsl+Vod9=1V,VBl的最小值为Vgs3+Vodl+Vod9=1.3V,Vod5的最大值为:VDD-(|Vgs5+Vod7|)=1.6V。因此,综合考虑合理设置其偏置电压VB4、VIN VG3、VG5、VBl分别为:0.8V、1.2V、1.79V、1.6V、2.21V。

|

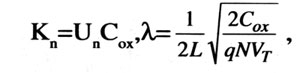

在进行电路设计时,首先需要手工估算宽长比W/I。,这可以根据C M 0 S管饱和电流公式IDS=Kn(W/L一)(VGs一VTN)2(1+λVDS)得到,式中器件跨导参数 |

其中COX为单位面积的氧化层电容,N为衬底掺杂浓度,Un为n沟道器件的表面迁移率。同理可计算P管参数。

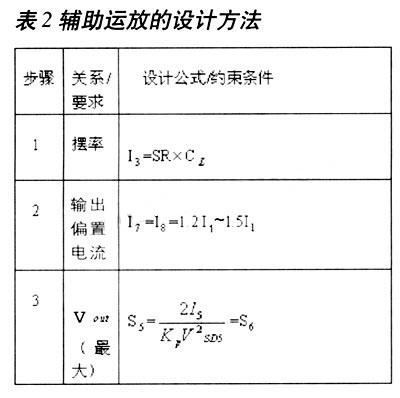

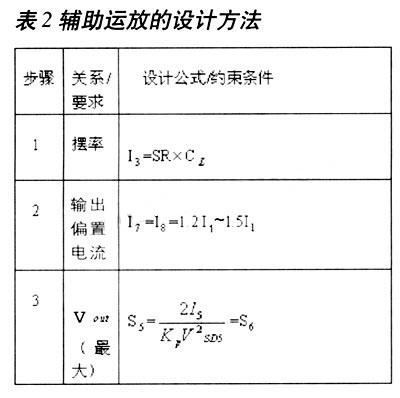

折叠式共源共栅辅助运放的设计方法如表2所示,其中设宽长比Sn=(W/L)n。 | | | |