9位100 MSPS流水线结构A/D转换器的设计

之一。本文介绍了流水线A/D转换器的基本原理,并构造了一个三级流水线结构的9位100 MSPS A/D转换器(ADC),采用Zarlink 0.6μm互补双极工艺模型对电路进行了模拟验证。

1 三级流水线A/D转换器电路设计

使用分级技术是解决高速高分辨率的一种方法。可以使用两级或多级高速、低分辨率子ADC组合起来,形成一个高速高分辨率的流水线ADC。

1.1 三级流水线A/D转换器工作原理

在基本A/D转换结构中,有些具备高速性能,有些具备高精度性能,没有能够同时达到高速高精度的要求。流水线ADC的出现在一定程度上解决了这个难题。流水线结构可以在采样速度和转换精度之间取得较好的平衡。图1是三级流水线ADC的结构。

由图1可知,流水线结构模/数转换器主要是由采样保持器、子ADC、子DAC及减法电路组成。输入模拟信号首先送入第一个采保电路(TH 1),TH1的输出信号输出给第一个的子ADC(ADC1)和第二个采保电路(TH2),ADC1将输入信号转换得到高3位数字信号,该高3位数据通过DAC(DA C1)还原成模拟量,再将该模拟量和TH2的输出一同输入到减法电路,并将差值由放大器放大一定倍数,便得到第一级模拟余量信号。此模拟余量将作为第二级转换电路的输入信号。重复上述步骤,得到次3位转换数据,依此类推。

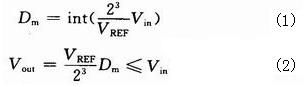

设输入信号为Vin,Vin通过3位ADC产生的数字量为Dm,3位DAC输一模拟量为Vout,则Vin,Dm和Vout的关系由式(1)、(2)决定。

由式(2)可知,3位DAC还原得到的Vout小于等于输入信号Vin,其差值就是包含低位数据位信息的模拟余量。为了使下一单元的ADC得到满幅输入,以降低对子ADC性能的要求,还需将此模拟余量乘以ADC量化单位的倒数,即将此模拟余量放大23倍后再送给下一级子转换器。

1.2 采样保持电路的设计与分析

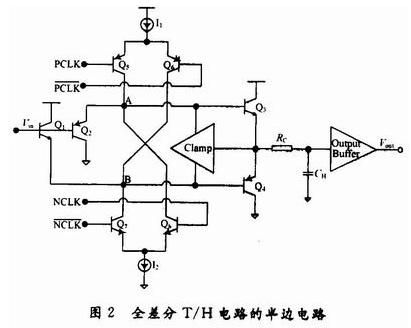

图2为全差分采样保持电路(T/H电路)的半边电路;图3为该T/H电路控制时钟信号。

当PCLK和NCLK信号为低电平时,T/H电路工作在采样模式,Q5,Q7导通,Q6,Q8截止,A节点电压升高,B节点电压降低,这时Q1~Q4均导通且工作在正向放大区,它们形成一个AB类缓冲器驱动保持电容CH。该输入电路结构具有输入偏置电流小、输入阻抗高、交调失真小的特点。当PCLK和NCLK信号为高电平时,T/H电路工作在保持模式,Q5,Q7截止,Q6,Q8导通,钳位电路(CLAMP)开始作用,使A节点电压钳位在VCH-VthN,使B结点的电压钳位在VCH+VthP(VthN和Vthp分别表示NPN管和PNP管的BE结导通屯压),也使A,B两节点呈现为低阻抗节点。此时Q1~Q4均截止,故而形成输入信号与保持电容之间的二重隔离,消除保持模式的信号馈通。

RC和CH构成一个低通滤波器,其截止频率会随负载而变化。为克服这一缺点,在输出端设计一个输出缓冲器。采样/保持电路的噪声特性主要来自于Q1~Q4的基极寄生电阻热噪声以及它们的散粒噪声和带宽限制电阻RC热噪声。电路设计时,选用大尺寸的器件来减小基极电阻Rb,使得基极寄生电阻热噪声最小化。将Q3,Q4偏置在较大的静态电流来最小化它们的散粒噪声,同时采样模式动态特性也要求Q3,Q4有大的静态电流,以减小VBE调制的影响。当该T/H电路被偏置在大电流时,它将有大的带宽,因此必须串联电阻RC来限制带宽以滤除高频噪声。大的偏置电流也要在功耗和性能之间进行折衷考虑。

1.3 子ADC的设计与分析

折叠型结构有比较器数量少、芯片复杂程度低、功耗较小的特点,具有较好的发展前景。将折叠结构ADC应用于流水线(Pipeline)技术中,构成流水线折叠式ADC,则可以提高其工作速度。折叠结构ADC的比较器个数与其分辨率成线性比例关系。1个n位分辨率的折叠结构ADC仅仅需要n个比较器。这不仅减小了芯片面积,而且降低了功耗。折叠单元电路是折叠式ADC的核心模块,其数学模型及波形模型如图4所示。

折叠单元电路工作原理如下;设折叠单元输入电压范围为-VR~+VR,如图4所示,输入信号同时送给跟随单元和比较器,跟随单元实现的功能是使得其输出端A,B分别跟随Vin+,Vin-中较高者和较低者;平移单元将跟随单元的输出电压进行平移,使其达到信号折叠的目的,如图4所示。其输出的电压信号Vout+,Vout-作为下一级折叠单元的输入信号。比较器输出的是格雷码数字输出,由于ADC最终要实现二进制码输出,所以还需要在后续电路中实现格雷码向二进制码的转换。

本文设计的A/D转换器电路采用2级折叠结构的子ADC,产生3位数字信号输出。2组折叠单元具有相同的结构,折叠单元接收差分模拟输入信号,产生1位输出数字信号,同时产生1对差分折叠模拟输出信号输出给下一级折叠单元。图5给出了折叠单元的结构原理,以及它的输入/输出波形。

- 14位125Msps模数转换器ADS5500及其应用 (03-06)

- 如何收敛高速ADC时序(03-09)

- 逐次逼近型 ADC:确保首次转换有效(03-20)

- 集成低功耗输入驱动器和基准电压源的16位6 MSPS SAR ADC系统(02-27)

- 具有抗混叠滤波器和184.32 MSPS采样速率的高性能中(04-23)

- 超低功耗16位IMSPS模数转换器(10-15)