超低功耗16位IMSPS模数转换器

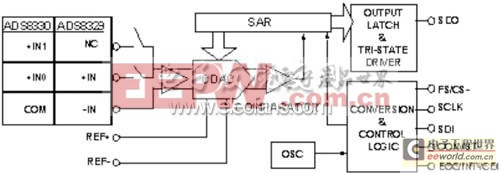

ADS8329和ADS8330属于同一个器件系列,他们是500kSPS ADS8327和ADS8328的升级延伸。所有产品均为引脚兼容,并提供了一个基于逐次逼近架构(SAR)的ADC。ADS8327和ADS8329均为单通道器件,而ADS8328和ADS8330为双通道器件。一个内部时钟用于对转换计时,但是也可以对该转换器进行编程,以利用串行接口的外部时钟。编程和数据传送均通过一个高速串行接口来完成。

图1 ADS8329/30结构图

如果转换正在使用内部时钟,那么外部时钟就应该被关闭。非同步时钟信号通常会引起基板失真,从而得到两种选项。如果ADC以内部时钟运行,那么就应该在转换之后读取数据,并且在数据传送完成以前,不应触发新的转换。如果该部件通过外部时钟运行,那么就可以在下一转换期间读取数据。外部时钟以两倍的转换速度运行,以确保数据传送在运行转换复写(overwrite)输出数据以前完成。

通过串行接口编程可实现多种额外的功能。一种是双通道产品的通道选择。这样,就可拥有一个自动触发器,其在前一个转换完成以后自动将转换起始信号 (CONVST) 初始化为4个转换时钟周期。利用链模式,数个同步采样ADC的数据可以通过一个串行接口读取。您可以在产品说明书中查看到其他的特性。

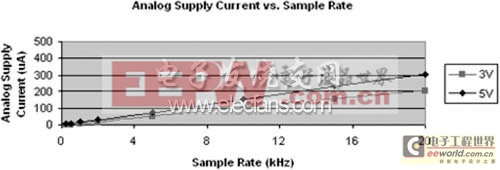

该转换器系列专门优化用以实现低功耗,以便具有多种功耗降低特性。在慢内部信号保持上电而快速(300ns)恢复模块被关闭的情况下,得以实施一个NAP模式。我们可以将2.7V电源电压的电流消耗从 5mA 降低至0.25mA,将5V电源电压的电流消耗从7mA降低至0.3mA。可以通过串行接口或触发CONVST信号来唤醒ADC。在正常运行状态下,CONVST信号将会立即冻结输入电压,并开始转换。在NAP模式下,ADC首先醒来,同时数据在6个时钟周期以后自动被冻结。

为了最小化开销,可将转换器置于一种AUTONAP模式。在该模式下,一旦转换完成,转换器就会自动地降低其电流消耗。因此,CONVST信号可以被用于唤醒ADC,并开始转换。在转换完成以后,ADC将再次降低其功耗。

如果ADC长期保持非使用状态,那么深度睡眠(PD)功能应该被用于充分降低ADC功耗。剩余的漏电流通常为4nA。图2和图3显示了NAP和PD运行中电流消耗与采样速率的关系。由于存在更长的唤醒时间,因此,深度睡眠运行模式应该只在低采样速率条件下才使用。对于100kSPS以上的采样速率而言,NAP功能更为有效。

图2 在NAP模式下,电流消耗与采样速率的关系

图3 在PD模式下,电流消耗与采样速率的关系

就节能而言,我们建议关闭ADC的外部时钟。否则,电流消耗可能会保持在1mA以上。ADS8329/30不同于一些有竞争力的产品,因为其可以被用于较宽的电源电压范围。在2.7V到5V的范围内可以选择模拟电源电压,而数字接口则可以始终在低至1.65V的电压下工作。

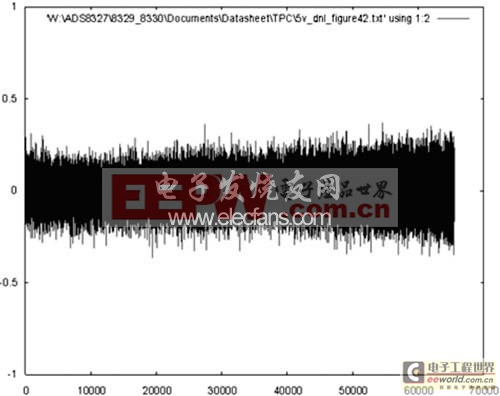

ADS8329/30的设计不仅是为了实现低功耗,还为了实现高性能。一个内部动态误差允许对较小调整进行校正,以及转换期间的散热效果,同时在转换结束时对其进行校正。该功能以及封装内的微调功能使差分线性度保持在±0.5LSB的范围内。紧密的差分线性度还有助于达到一个较好的积分线性。图 4和图 5 显示了这种典型的线性度。

- RS-485网络设计降低功耗问题(01-26)

- 低功耗CMOS电压基准源的设计(08-27)

- 一种新型低功耗两级运算放大器的实现(01-20)

- 创建理想的低功耗设计(01-14)

- 新一代电池供电装置的超低功耗设计(07-18)

- 基于绝热逻辑的低功耗乘法器电路设计(07-23)