DSP电源管理技术加快设计进度

时间:02-02

来源:EDN

点击:

许多电池供电的手持系统都要求具备数字信号处理功能,设计这种产品时,我们必须高度重视功耗问题。

选择既能符合计算能力要求又在功率预算之内的DSP是决定设计在市场成败的关键,否则,设计小组必须劳民伤财重新设计。

不过,大多数设计工程师已经痛苦地了解到,传统DSP功耗估算方法最多也只能获得近似值,因此我们需要用软件来管理功耗并估算功耗的新技术。

数据表不够用

以前,设计小组选择处理器时首先要查看备选DSP的数据表。以 mA/MIP 或mA/MHz 为单位的测量值通常与芯片的最大 IDD 配套提供。几乎所有数据表都提供上述信息。

上述数据的问题在于,功耗很大程度上取决于应用本身,而数据表中的统计数据往往不能完全符合实际应用。

半导体公司认识到上述问题,通常只给出基本情况,供估算功耗数值参考。举例来说,常见的 TI DSP 会给出以下工作情况:CPU 执行 75% 双 MAC 和 25% ADD,数据总线活动适中(正弦波形图表)。CPU 及 CLKGEN (DPLL) 域处于工作状态中。

除非设计小组的应用情况与上述描述一致,否则数据表中的数据仅用于比较同一制造商推出的类似芯片。事实上,其他半导体公司很可能会在不同情况下测量功耗。

对那些功耗限制更严的设计人员来说有些状况让数据表的价值更成问题。

DSP是复杂的芯片,其包括休眠模式和断电模式等节电功能。上述功能会将单次估算中的误差加以放大。

数据表未考虑到功耗实际上由两部分组成:工作在内核电压源上的处理器和工作在 I/O 电源上的外设都涉及功耗问题。

设计小组希望用不同的实施方法和平台比较功耗。

这些挑战造成的后果就是,设计小组往往需要构建原型板,并根据不同处理器、实施方法及平台等因素对功耗加以估算。上述方法尽管要花很多时间而且成本不菲,但至少还能为我们提供比较精确的数据。

变量测量

我们对估算不同情况及实施方法下的功耗所用的方法已经有了较好的了解。只有经过细分,并根据实际测量得出的数据才会更加有用。具体过程通常如下:

将芯片分为子系统;

独立执行每个子系统;

用减法分析来确定每个子系统的功耗;

确定每个子系统的最大功耗及闲置功耗;

用内插法估算子系统功耗;

最后用叠加法估算芯片功耗。

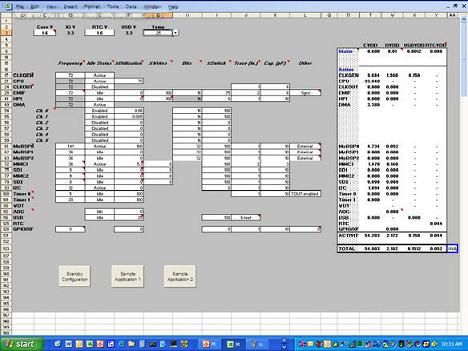

我们通常将经测量得出的数据连同制造商给出的数据(如内核电压)制成电子数据表,并通过适当运算进行估算。如图 1 所示,右侧的灰白部分即为功耗估算结果。

选择既能符合计算能力要求又在功率预算之内的DSP是决定设计在市场成败的关键,否则,设计小组必须劳民伤财重新设计。

不过,大多数设计工程师已经痛苦地了解到,传统DSP功耗估算方法最多也只能获得近似值,因此我们需要用软件来管理功耗并估算功耗的新技术。

数据表不够用

以前,设计小组选择处理器时首先要查看备选DSP的数据表。以 mA/MIP 或mA/MHz 为单位的测量值通常与芯片的最大 IDD 配套提供。几乎所有数据表都提供上述信息。

上述数据的问题在于,功耗很大程度上取决于应用本身,而数据表中的统计数据往往不能完全符合实际应用。

半导体公司认识到上述问题,通常只给出基本情况,供估算功耗数值参考。举例来说,常见的 TI DSP 会给出以下工作情况:CPU 执行 75% 双 MAC 和 25% ADD,数据总线活动适中(正弦波形图表)。CPU 及 CLKGEN (DPLL) 域处于工作状态中。

除非设计小组的应用情况与上述描述一致,否则数据表中的数据仅用于比较同一制造商推出的类似芯片。事实上,其他半导体公司很可能会在不同情况下测量功耗。

对那些功耗限制更严的设计人员来说有些状况让数据表的价值更成问题。

DSP是复杂的芯片,其包括休眠模式和断电模式等节电功能。上述功能会将单次估算中的误差加以放大。

数据表未考虑到功耗实际上由两部分组成:工作在内核电压源上的处理器和工作在 I/O 电源上的外设都涉及功耗问题。

设计小组希望用不同的实施方法和平台比较功耗。

这些挑战造成的后果就是,设计小组往往需要构建原型板,并根据不同处理器、实施方法及平台等因素对功耗加以估算。上述方法尽管要花很多时间而且成本不菲,但至少还能为我们提供比较精确的数据。

变量测量

我们对估算不同情况及实施方法下的功耗所用的方法已经有了较好的了解。只有经过细分,并根据实际测量得出的数据才会更加有用。具体过程通常如下:

将芯片分为子系统;

独立执行每个子系统;

用减法分析来确定每个子系统的功耗;

确定每个子系统的最大功耗及闲置功耗;

用内插法估算子系统功耗;

最后用叠加法估算芯片功耗。

我们通常将经测量得出的数据连同制造商给出的数据(如内核电压)制成电子数据表,并通过适当运算进行估算。如图 1 所示,右侧的灰白部分即为功耗估算结果。

图1. 电子数据表有一定的用处,但仍不能反映实际情况 这种方法与数据表值比较法相比尽管有一定改进,但仍需进一步完善。举例来说,我们不妨假设主要用于过滤应用的 DSP,其工作时间约占 20%,待机时间约占80%。 目前的 DSP 需要考虑到占空比问题,这有助于节电。举例来说,芯片不工作时,电压可降至待机数值。频率在 CMOS 功耗中起主要作用,如果芯片不参与过滤工作,那么我们就能降低频率。 电源优化技术 TI 等半导体厂商努力推出芯片级电源控制技术。以前设计小组是无法应用这种特性的。现在,设计人员能通过软件发挥电源优化技术的优势。 为了说明如何实现上述工作,我们不妨先来看看设计小组能采用哪些优化性能的方法。 在芯片自身内部,系统设计人员能采用深度休眠模式、动态电压和频率缩放等技术,而且还能在芯片闲置时关闭不必要的资源。 我们还能在系统启动过程中节约大量电力。通常说来,启动过程中会开启所有系统,不过我们可以让那些应用及启动过程中不用的部分关闭或保持闲置状态。 我们在软件代码优化时也要想到功耗问题。通常的规律是,我们应以尽可能小的占用空间集成尽可能多的必需功能,这样可以缩减存储器的占用面积。不过,由于应用不得不更频繁的执行代码,这种做法往往会导致功耗的加大。 编写代码时还应减少指令存取的数量,并优化缓存和内部指令缓冲。上述措施都有助于节约DSP的工作模式时间,并最大化闲置时间,以此来降低频率和电压。 我们还能用其他技术来实现系统级控制,包括: 认真选择组件 尽可能减少组件数量 首先采用内部存储器来最小化芯片间的功率损耗 对于启动或低速运算以及偶尔用到的功能采用外部存储器 启动后给启动存储器断电 新一代电源控制技术 通常说来,半导体厂商在芯片中内置的节电功能会自动工作,举例来说,芯片进入闲置状态后电压和频率就会自动降低。 不过,我们现在有了更尖端的技术,系统设计人员现在能对 DSP BIOS 进行工作,从而进一步加强电源管理。 自动的电压或频率缩放是一种有用的特性。不过 DSP 的内核电压快速变动往往会对外设造成意料不到的影响。操作系统的时基可能会因频率变动而受到影响,有些外设驱动程序可能需要了解 频率和电源状态的变化,这样才能继续有效工作。 操作系统调度程序的有效性也会因为频率缩放而受影响。通常说来,系统应进行协调,以确保安全的电压和频率控制,适当地进入闲置状态。 半导体厂商通过创建DSP BIOS功率调整程序库,可实现更高级的功耗控制,同时还能确保避免因电压和频率缩放而发生问题。通过GPIO引脚向外设发送消息,我们还能将上述控制技术从芯片延伸到外设。 图2显示了功率调整例程的实例(如下图中的 PSL),设计人员通过代码编写,可从程序库中直接调用。 |

- 单片式降压型稳压器为DSP提供片内电源排序(01-09)

- 什么是PCI总线?其接口芯片的应用(01-26)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)

- 具有多个电压轨的FPGA和DSP电源设计实例(二) (05-22)

- 基于DSP和CPLD的移相全桥软开关电源数字控制器(06-02)