仪表放大器电路设计

时间:01-27

来源:EDN

点击:

0 引 言

智能仪表仪器通过传感器输入的信号,一般都具有"小"信号的特征:信号幅度很小(毫伏甚至微伏量级),且常常伴随有较大的噪声。对于这样的信号,电路处理的第一步通常是采用仪表放大器先将小信号放大。放大的最主要目的不是增益,而是提高电路的信噪比;同时仪表放大器电路能够分辨的输入信号越小越好,动态范围越宽越好。仪表放大器电路性能的优劣直接影响到智能仪表仪器能够检测的输入信号范围。本文从仪表放大器电路的结构、原理出发,设计出四种仪表放大器电路实现方案,通过分析、比较,给出每一种电路方案的特点,为电路设计爱好者、学生进行电子电路实验提供一定的参考。

1 仪表放大器电路的构成及原理

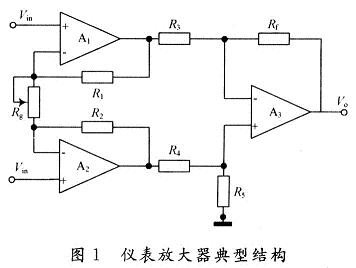

仪表放大器电路的典型结构如图1所示。它主要由两级差分放大器电路构成。其中,运放A1,A2为同相差分输入方式,同相输入可以大幅度提高电路的输入阻抗,减小电路对微弱输入信号的衰减;差分输入可以使电路只对差模信号放大,而对共模输入信号只起跟随作用,使得送到后级的差模信号与共模信号的幅值之比(即共模抑制比CMRR)得到提高。这样在以运放A3为核心部件组成的差分放大电路中,在CMRR要求不变情况下,可明显降低对电阻R3和R4,RF和R5的精度匹配要求,从而使仪表放大器电路比简单的差分放大电路具有更好的共模抑制能力。在R1=R2,R3=R4,Rf=R5的条件下,图1电路的增益为:G=(1+2R1/Rg)(Rf/R3)。由公式可见,电路增益的调节可以通过改变Rg阻值实现。

2 仪表放大器电路设计

2.1 仪表放大器电路实现方案

目前,仪表放大器电路的实现方法主要分为两大类:第一类由分立元件组合而成;另一类由单片集成芯片直接实现。根据现有元器件,文中分别以单运放LM741和OP07,集成四运放LM324和单片集成芯片AD620为核心,设计出四种仪表放大器电路方案。

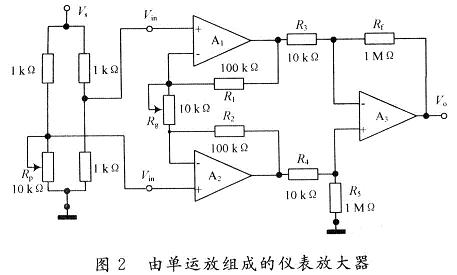

方案1 由3个通用型运放LM741组成三运放仪表放大器电路形式,辅以相关的电阻外围电路,加上A1,A2同相输入端的桥式信号输入电路,如图2所示。

图2中的A1~A3分别用LM741替换即可。电路的工作原理与典型仪表放大器电路完全相同。方案2 由3个精密运放OP07组成,电路结构与原理和图2相同(用3个OP07分别代替图2中的A1~A3)。

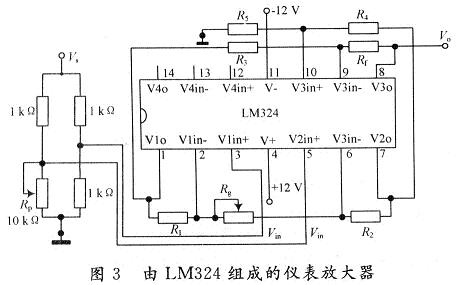

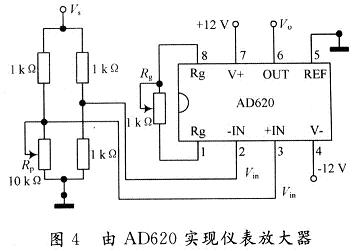

方案3 以一个四运放集成电路LM324为核心实现,如图3所示。它的特点是将4个功能独立的运放集成在同一个集成芯片里,这样可以大大减少各运放由于制造工艺不同带来的器件性能差异;采用统一的电源,有利于电源噪声的降低和电路性能指标的提高,且电路的基本工作原理不变。方案4 由一个单片集成芯片A13620实现,如图4所示。它的特点是电路结构简单:一个AD620,一个增益设置电阻Rg,外加工作电源就可以使电路工作,因此设计效率最高。图4中电路增益计算公式为:G=49.4K/Rg+1。

2.2 性能测试与分析

实现仪表放大器电路的四种方案中,都采用4个电阻组成电桥电路的形式,将双端差分输入变为单端的信号源输入。性能测试主要是从信号源Vs的最大输入和Vs最小输入、电路的最大增益及共模抑制比几方面进行仿真和实际电路性能测试。测试数据分别见表1和表2。其中,Vs最大(小)输入是指在给定测试条件下,使电路输出不失真时的信号源最大(小)输入;最大增益是指在给定测试条件下,使输出不失真时可以实现的电路最大增益值。共模抑制比由公式KCMRR=20|g | AVd/AVC|(dB)计算得出。

说明:

(1)f为Vs输入信号的频率;

(2)表格中的电压测量数据全部以峰峰值表示;

(3)由于仿真器件原因,实验中用Multisim对方案3的仿真失效,表1中用"-"表示失效数据;

(4)表格中的方案1~4依次分别表示以LM741,OP07,LM324和AD620为核心组成的仪表放大器电路。

由表1和表2可见,仿真性能明显优于实际测试性能。这是因为仿真电路的性能基本上是由仿真器件的性能和电路的结构形式确定的,没有外界干扰因素,为理想条件下的测试;而实际测试电路由于受环境干扰因素(如环境温度、空间电磁干扰等)、人为操作因素、实际测试仪器精确度、准确度和量程范围等的限制,使测试条件不够理想,测量结果具有一定的误差。在实际电路设计过程中,仿真与实际测试各有所长。一般先通过仿真测试,初步确定电路的结构及器件参数,再通过实际电路测试,改进其具体性能指标及参数设置。这样,在保证电路功能、性能的前提下,大大提高电路设计的效率。

智能仪表仪器通过传感器输入的信号,一般都具有"小"信号的特征:信号幅度很小(毫伏甚至微伏量级),且常常伴随有较大的噪声。对于这样的信号,电路处理的第一步通常是采用仪表放大器先将小信号放大。放大的最主要目的不是增益,而是提高电路的信噪比;同时仪表放大器电路能够分辨的输入信号越小越好,动态范围越宽越好。仪表放大器电路性能的优劣直接影响到智能仪表仪器能够检测的输入信号范围。本文从仪表放大器电路的结构、原理出发,设计出四种仪表放大器电路实现方案,通过分析、比较,给出每一种电路方案的特点,为电路设计爱好者、学生进行电子电路实验提供一定的参考。

1 仪表放大器电路的构成及原理

仪表放大器电路的典型结构如图1所示。它主要由两级差分放大器电路构成。其中,运放A1,A2为同相差分输入方式,同相输入可以大幅度提高电路的输入阻抗,减小电路对微弱输入信号的衰减;差分输入可以使电路只对差模信号放大,而对共模输入信号只起跟随作用,使得送到后级的差模信号与共模信号的幅值之比(即共模抑制比CMRR)得到提高。这样在以运放A3为核心部件组成的差分放大电路中,在CMRR要求不变情况下,可明显降低对电阻R3和R4,RF和R5的精度匹配要求,从而使仪表放大器电路比简单的差分放大电路具有更好的共模抑制能力。在R1=R2,R3=R4,Rf=R5的条件下,图1电路的增益为:G=(1+2R1/Rg)(Rf/R3)。由公式可见,电路增益的调节可以通过改变Rg阻值实现。

|

2 仪表放大器电路设计

2.1 仪表放大器电路实现方案

目前,仪表放大器电路的实现方法主要分为两大类:第一类由分立元件组合而成;另一类由单片集成芯片直接实现。根据现有元器件,文中分别以单运放LM741和OP07,集成四运放LM324和单片集成芯片AD620为核心,设计出四种仪表放大器电路方案。

方案1 由3个通用型运放LM741组成三运放仪表放大器电路形式,辅以相关的电阻外围电路,加上A1,A2同相输入端的桥式信号输入电路,如图2所示。

|

图2中的A1~A3分别用LM741替换即可。电路的工作原理与典型仪表放大器电路完全相同。方案2 由3个精密运放OP07组成,电路结构与原理和图2相同(用3个OP07分别代替图2中的A1~A3)。

方案3 以一个四运放集成电路LM324为核心实现,如图3所示。它的特点是将4个功能独立的运放集成在同一个集成芯片里,这样可以大大减少各运放由于制造工艺不同带来的器件性能差异;采用统一的电源,有利于电源噪声的降低和电路性能指标的提高,且电路的基本工作原理不变。方案4 由一个单片集成芯片A13620实现,如图4所示。它的特点是电路结构简单:一个AD620,一个增益设置电阻Rg,外加工作电源就可以使电路工作,因此设计效率最高。图4中电路增益计算公式为:G=49.4K/Rg+1。

|

|

2.2 性能测试与分析

实现仪表放大器电路的四种方案中,都采用4个电阻组成电桥电路的形式,将双端差分输入变为单端的信号源输入。性能测试主要是从信号源Vs的最大输入和Vs最小输入、电路的最大增益及共模抑制比几方面进行仿真和实际电路性能测试。测试数据分别见表1和表2。其中,Vs最大(小)输入是指在给定测试条件下,使电路输出不失真时的信号源最大(小)输入;最大增益是指在给定测试条件下,使输出不失真时可以实现的电路最大增益值。共模抑制比由公式KCMRR=20|g | AVd/AVC|(dB)计算得出。

说明:

(1)f为Vs输入信号的频率;

(2)表格中的电压测量数据全部以峰峰值表示;

(3)由于仿真器件原因,实验中用Multisim对方案3的仿真失效,表1中用"-"表示失效数据;

(4)表格中的方案1~4依次分别表示以LM741,OP07,LM324和AD620为核心组成的仪表放大器电路。

由表1和表2可见,仿真性能明显优于实际测试性能。这是因为仿真电路的性能基本上是由仿真器件的性能和电路的结构形式确定的,没有外界干扰因素,为理想条件下的测试;而实际测试电路由于受环境干扰因素(如环境温度、空间电磁干扰等)、人为操作因素、实际测试仪器精确度、准确度和量程范围等的限制,使测试条件不够理想,测量结果具有一定的误差。在实际电路设计过程中,仿真与实际测试各有所长。一般先通过仿真测试,初步确定电路的结构及器件参数,再通过实际电路测试,改进其具体性能指标及参数设置。这样,在保证电路功能、性能的前提下,大大提高电路设计的效率。

- 如何构建仪表放大器(07-08)

- 使用仪表放大器的高性能加法器(10-30)

- 采用仪表放大器的0V压降分流器(01-29)

- AD7794在高精度低功耗测量装置中的应用(04-14)

- 一个电路即可满足系统解析度和12位精度要求(04-27)

- 被完全误解的三运放仪表放大器(05-24)