被完全误解的三运放仪表放大器

图1所示的三运放仪表放大器看似为一种简单的结构,因为它使用已经存在了几十年的基本运算放大器(op amp)来获得差动输入信号。运算放大器的输入失调电压误差不难理解。运算放大器开环增益的定义没有改变。运算放大器共模抑制(CMR)的简单方法自运算放大器时代之初就已经有了。那么,问题出在哪里呢?

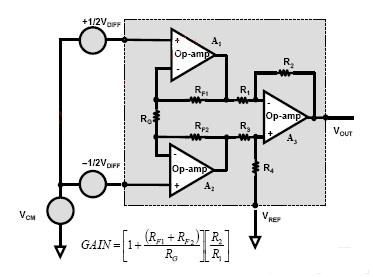

图1:三运放仪表放大器,其VCM为共模电压,而VDIFF为相同仪表放大器的差动输入。

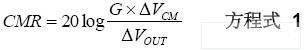

单运算放大器和仪表放大器的共享CMR方程式如下:

本方程式中,G相当于系统增益,VCM为相对于接地电压同样施加于系统输入端的变化电压,而VOUT为相对于变化VCM值的系统输出电压变化。

在CMR方面,运算放大器的内部活动很简单,其失调电压变化是唯一的问题。就仪表放大器而言,有两个影响器件CMR的因素。第一个也是最重要的因素是,涉及第三个放大器(图1,A3)电阻比率的平衡问题。例如,如果R1等于R3,R2等于R4,则理想状况下的三运放仪表放大器CMR为无穷大。然而,我们还是要回到现实世界中来,研究R1、R2、R3 和R4与仪表放大器CMR的关系。

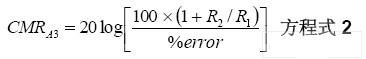

具体而言,将R1:R2同R3:R4匹配至关重要。结合A3,这4个电阻从A1和A2的输出减去并增益信号。电阻比之间的错配会在A3输出端形成误差。方程式2在这些电阻关系方面会形成CMR误差:

例如,如果R1、R2、R3和R4接近相同值,且R3:R4等于R1/R2的1.001,则该0.1%错配会带来仪表放大器CMR的降低,从理想水平降至66dB级别。

根据方程式1,仪表放大器CMR随系统增益的增加而增加。这是一个非常好的特性。方程式1可能会激发仪表放大器设计人员确保有许多可用增益,但是这种方法存在一定的局限性。A1和A2开环增益误差和噪声。放大器的开环增益等于20log(ΔVOUT/ΔVOS)。随着A1和A2增益的增加,放大器开环增益失调误差也随之增加。A1和A2的输出振幅变化一般涵盖电源轨。仪表放大器增益更高的情况下,运算放大器的开环增益误差和噪声占主导。通过RSS公式,这些误差降低了更高增益下的仪表CMR。因此,您会看到仪表放大器的CMR性能值往往会在更高增益时达到最大值。

因此,从CMR角度来看,仪表放大器就像是一个在不同系统增益下器件各部分都诱发CMR误差的系统。当您对器件的内部原理进行研究时,它便不再如此神秘。您把各个部分都分开来,就会一目了然。

- 三运放仪表放大器在设计中的应用(07-21)

- 三运放仪表放大器(INA)共模范围可能会是一个难题(07-21)

- 三运放差动放大器电路图(11-15)

- 如何构建仪表放大器(07-08)

- 使用仪表放大器的高性能加法器(10-30)

- 采用仪表放大器的0V压降分流器(01-29)