降低高速DSP系统设计中的电源噪声

时间:01-15

来源:EDN

点击:

|

随着芯核和I/O电压工作不同频率,必须用合适大小的电容器去耦电源。在此实例中,用下面的公式计算,计算的芯核电容为0.0078礔,对于216mA I/O 电流所需电容为0.22礔:C=I(dv/dt)

其中I为峰值电流,dv为最大所允许的纹波电压(假定10mV),dt为上升时间(假定1ns,OMAP5910典型值)。

所以,芯核电容C=78mA×(1ns/10mv)=0.0078礔

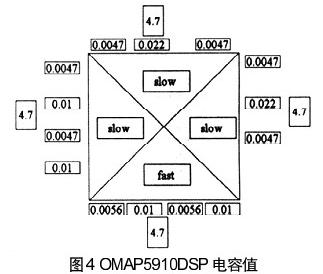

在OMAP5910 BGA 封装中,对于每个区域的4个电容器都有足够的空间,没有一个是用于每个芯核电源引脚的。因此,为了去耦芯核电压引脚,最好选择两个电容器,其总值为 0.0078礔(配置两个0.0047礔陶瓷电容器,以使从引脚到地有最短距离)。

必须考虑开关频率。芯核部分在150MHz开关转换,而8个I/O引脚在75MHz开关转换。可以用另外两个电容器位置来去耦I/O电压引脚(即用两个自谐波振频率75MHz以上的0.01礔陶瓷电容器提供0.022礔)。

体电容器值

在此实例中,DSP总芯核电压电流为338mA。用上面的公式计算电容为0.0338礔。做为体电容应该是10倍去耦电容值,大约为0.39礔。对于I/O电压,进行同样的处理,得到0.84礔电容,给出总电容1.23礔。对于体电容器,每个提供3.075礔(1.23礔除以4,然后乘以10),应该把它加到每个区域上。现在可得到的最小体电容值是做为表面贴装元件的4.7礔,此电容值在本例中工作良好。如果没有表面贴装电解电容,应选择钽体电容器。对于4个区域的每个区域去耦和体电容值可以用这种方法计算,并示于图4。

发布者:博子

- 单片式降压型稳压器为DSP提供片内电源排序(01-09)

- 什么是PCI总线?其接口芯片的应用(01-26)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)

- 具有多个电压轨的FPGA和DSP电源设计实例(二) (05-22)

- 基于DSP和CPLD的移相全桥软开关电源数字控制器(06-02)