快速创建存储器接口的设计

时间:10-22

来源:EDN

点击:

|

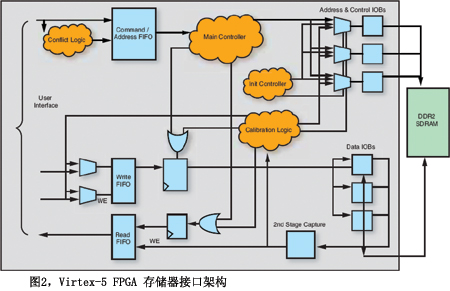

用于地址、控制和数据的物理层接口在 IOB 中实现。采集 DQ 时,存储器 DQS 会采集相应 DQ 并以此 DQS 的延迟形式将其寄存。此数据然后在触发器的第二级与系统的时钟域同步。I/O 模块中的输入串行器/解串器功能用于读数据采集,第一对触发器将数据从延迟 DQS 传输至系统时钟域。该技术涉及到 75 ps tap 延迟 (IODELAY) 单元的应用,在由校准逻辑实现的校准程序中,这些延迟单 元会有所变化。系统初始化期间会执行此校准程序,以设置 DQS、数据和系统时钟之间的最佳相位,从而使时序余量达到最大化。

此设计还包括其他方面,如整体控制器状态机的逻辑生成和用户接口。为方便 FPGA 设计人员轻松实现整个设计,Xilinx 开发了存储器接口生成器。

设计及与 MIG 的集成

将包括存储器控制器状态机在内的所有构建模块集成到一起,对于设计的完整性具有重要意义。控制器状态机因存储器架构和系统参数的不同而异。状态机代码也可能很复杂,取决于许多变量,如架构、数据总线宽度、深度、存取算法和数据与选通脉冲比等。

使用 MIG 可生成完整的设计,该软件工具作为 ISE软件 CORE Generator参考设计和知识产权作品套件之一部分,可从 Xilinx 免费获取。MIG 的设计流程与传统 FPGA 的设计流程非常相似。对于设计人员,MIG 的优点是不必再为物理层接口或存储器控制器从头生成 RTL 代码。

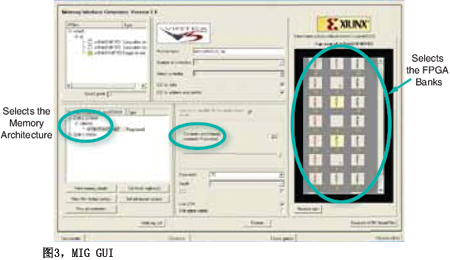

可以使用MIG 的GUI设置系统和存储器参数(图3)。例如,选定FPGA器件、封装和速度级别后,可以选择存储器架构并挑选实际的存储器器件或双列直插存储器模块 (DIMM)。同是这一个GUI,还可用于选择总线宽度和时钟频率。其他选项可对时钟控制方法、CAS延迟、突发长度和引脚分配进行控制。

|

MIG 工具可在数分钟内生成 RTL 和 UCF 文件,二者各为 HDL 代码和约束文件。这些文件是用一个经过硬件验证的参考设计库生成的,并根据用户输入进行了修改。

有进一步修改 RTL 代码的完全的灵活性。与提供"黑匣子"实现方法的其他解决方案不同,此设计中的代码未经加密,设计人员可对设计随意修改并进一步定制。输出文件按模块分类,适用于此设计的不同构建模块:用户接口、物理层或控制器状态机。例如,可定制对存取算法进行控制的状态机。修改可选代码后,可再次进行仿真,以验证整体设计的功能。

MIG 还可生成具有存储器校验功能的可综合测试平台。该测试平台是一个设计示例,用于 Xilinx 基础设计的功能仿真和硬件验证。

设计的最后阶段是导入 ISE 项目中的 MIG 文件,将其与 FPGA 设计的其余文件合并,然后进行综合、布局和布线,必要时还会运行其他时序仿真,最后进行硬件验证。MIG 软件还会生成一个批处理文件,包括相应的综合、映射以及布局和布线选项,以帮助优化生成最终的 bit 文件。

开发板和套件

参考设计的硬件验证是确保解决方案严密可靠的最终重要步骤。Xilinx 已验证了 Spartan-3 系列和 Virtex-5 FPGA 的存储器接口设计。表 1 所示为各种开发板所支持的存储器接口。

|

开发板的范围涵盖从低成本 Spartan-3 系列 FPGA 实现到 Virtex-5 FPGA 系列所提供的高性能解决方案。

- 什么是FSL总线(01-03)

- Xilinx All Programmable RFSoC 背景资料(02-22)

- 基于FPGA的∑-△D/A转换器的设计与实现(04-23)

- 发射应用中多个高速复用DAC的同步(06-23)

- 一种锁定相位编程可调全数字锁相环设计(06-24)

- AD6620工作原理/在中频数字化直扩接收机应用(06-25)