一种锁定相位编程可调全数字锁相环设计

时间:06-24

来源:互联网

点击:

1 引 言

锁相技术在信号处理、调制解调、时钟同步、倍频、频率综合等领域都得到了广泛的应用。目前锁相技术的实现主要有模拟锁相环(APLL)、全数字锁相环(DPLL)、模拟数字混合锁相环与延迟锁相环(DLL)四种。全数字锁相环(DPLL)具有精度高且不受温度和电压影响,环路带宽和中心频率编程可调等优点.得到了广泛应用。

经典全数字锁相环路由数字鉴相器、K模可逆计数器、脉冲加减控制电路和N分频器4部分组成。在输入信号频率稳定条件下,锁相环锁定时输出信号与输入信号正交。在通信和其他很多应用领域,不仅需要输出信号与输入信号保持正交关系,有时也需要他们保持某些特定的相位差。本文在经典结构基础上稍做改进,提出了一种输出信号与输入信号的锁定相位编程可调的全数字锁相环路的设计。经过计算机仿真分析、FPGA实现及板级系统实验,证明了系统的可行性和可靠性。

2 经典数字锁相环路结构及工作原理

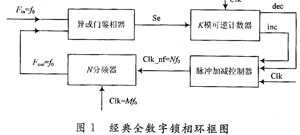

图1示出了采用异或门鉴相器的经典数字锁相环路的结构框图。各个模块的结构和功能如下:

2.1 异或门鉴相器

异或门鉴相器将锁相环路输入信号Fin与输出信号Fout做减法,输出相位差Se作为K模可逆计数器的计数方向信号。当环路锁定时输出信号与输入信号稳定正交,Se是一占空比为50%的方波信号。

2.2 K模可逆计数器

K模可逆计数器产生进位和借位脉冲并起到环路滤波的作用。他由系统时钟Clk(频率M?0)控制对异或门鉴相器输出的相位差信号Se进行采样计数,当Se为低电平时做加计数,计数值达到预定模值K时输出进位脉冲inc同时计数器回零;当Se为高电平时做减计数,计数值为零时输出借位脉冲dec同时计数器置K。当环路锁定Se是一占空比为50%的方波信号时,交替输出进位和借位脉冲。计数器模值K的大小决定了环路进入锁定的时间,K值越大环路锁定时间越长。

2.3 脉冲加减控制器和N分频器

脉冲加减控制器实现数字压控振荡器的功能。当K模可逆计数器有进位脉冲输出时,控制器捕获该脉冲信号,并在输出信号Clk_nf中插入一个系统时钟周期的脉冲,N分频器对Clk_nf信号分频,从而使环路输出信号Fout超前一个时钟周期的相位;同样的,当有借位脉冲时控制器在Clk_nf减去一个系统时钟周期的脉冲,从而使输出信号Fout滞后一个时钟周期,这样就起到了相位调节的作用。当环路锁定时交替出现的进位和借位脉冲调相作用相互抵消,输出时钟Fout 稳定。

3 改进的数宇锁相环结构及工作原理

3.1 改进的数字锁相环设计思路及其结构

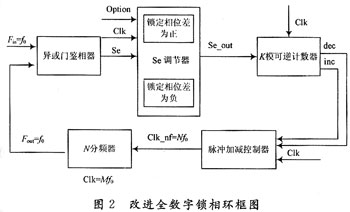

如图2所示,在异或门鉴相器与K模可逆计数器之间插入一个Se的调节器对Se的波形进行调节,即给了K模计数器一个虚假的输出信号与输入信号的相位差Se_out。当伪相位差信号Se_out为方波时输出与输入信号锁定在一个特定的相位。

3.2 Se调节器的设计实现

我们假定输出信号Fout与输入信号Fin正交时二者相差为零。设输出信号滞后于输入信号环路锁定相位羞为负,输出信号超前于输入信号环路锁定相位差为正。用Option信号选择锁定方式并输入相位差值。分别分析锁定相位差为负和锁定相位差为正环路进入锁定时各个信号之间的相位关系,很直观地得到Se调节器的实现方法。

3.2.1 锁定相位差为负Se调节器的设计实现

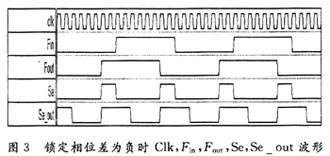

系统时钟Clk,输入信号Fin、输出信号Fout,相位差信号Se与伪相位差信号Se_out的相位关系如图3所示。伪相位差信号Se_out为一占空比为50%的方波,系统锁定。此时输出信号滞后于输入信号一定的相位,记为off-set。相位差信号Se高电平占空比低于伪相位差信号Se_out高电平占空比的值就是输出信号滞后于输人信号的相位offset。Se调节器要完成的工作就是将Se调整为Se_out的波形,即将Se为低电平宽度为offset的区域转换成高电平。具体实现为:设计一个预置值为offset的计数器。在Se为高电平时Se保持不变,同时计数器计数值保持为O,在Se由高电平变为低电平后开始加计数,当计数值未达到预置值offset。时Se仍保持为高电平,当计数值超过预置值offset时,将Se置低电平,这样得到的波形就是所需要的se_out。

3.2.2 锁定相位差为正Se调节器的设计实现

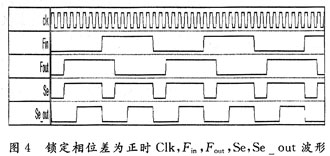

系统时钟Clk、输入信号Fin,输出信号Fout,相位差信号Se与伪相位差信号Se_out的相位关系如图4所示。与输出信号滞后于输人信号环路锁定类似:设计一个预置值为offset的计数器。在Se为低电平时Se保持不变,同时计数器计数值保持为O,在Se由低电平变为高电平后开始加计数,当计数值未达到预置值offset时Se仍保持为低电平,当计数值超过预置值offset时,将Se置高电平,这样得到的波形就是所需要的Se_out。

3.3

锁相技术在信号处理、调制解调、时钟同步、倍频、频率综合等领域都得到了广泛的应用。目前锁相技术的实现主要有模拟锁相环(APLL)、全数字锁相环(DPLL)、模拟数字混合锁相环与延迟锁相环(DLL)四种。全数字锁相环(DPLL)具有精度高且不受温度和电压影响,环路带宽和中心频率编程可调等优点.得到了广泛应用。

经典全数字锁相环路由数字鉴相器、K模可逆计数器、脉冲加减控制电路和N分频器4部分组成。在输入信号频率稳定条件下,锁相环锁定时输出信号与输入信号正交。在通信和其他很多应用领域,不仅需要输出信号与输入信号保持正交关系,有时也需要他们保持某些特定的相位差。本文在经典结构基础上稍做改进,提出了一种输出信号与输入信号的锁定相位编程可调的全数字锁相环路的设计。经过计算机仿真分析、FPGA实现及板级系统实验,证明了系统的可行性和可靠性。

2 经典数字锁相环路结构及工作原理

图1示出了采用异或门鉴相器的经典数字锁相环路的结构框图。各个模块的结构和功能如下:

|

异或门鉴相器将锁相环路输入信号Fin与输出信号Fout做减法,输出相位差Se作为K模可逆计数器的计数方向信号。当环路锁定时输出信号与输入信号稳定正交,Se是一占空比为50%的方波信号。

2.2 K模可逆计数器

K模可逆计数器产生进位和借位脉冲并起到环路滤波的作用。他由系统时钟Clk(频率M?0)控制对异或门鉴相器输出的相位差信号Se进行采样计数,当Se为低电平时做加计数,计数值达到预定模值K时输出进位脉冲inc同时计数器回零;当Se为高电平时做减计数,计数值为零时输出借位脉冲dec同时计数器置K。当环路锁定Se是一占空比为50%的方波信号时,交替输出进位和借位脉冲。计数器模值K的大小决定了环路进入锁定的时间,K值越大环路锁定时间越长。

2.3 脉冲加减控制器和N分频器

脉冲加减控制器实现数字压控振荡器的功能。当K模可逆计数器有进位脉冲输出时,控制器捕获该脉冲信号,并在输出信号Clk_nf中插入一个系统时钟周期的脉冲,N分频器对Clk_nf信号分频,从而使环路输出信号Fout超前一个时钟周期的相位;同样的,当有借位脉冲时控制器在Clk_nf减去一个系统时钟周期的脉冲,从而使输出信号Fout滞后一个时钟周期,这样就起到了相位调节的作用。当环路锁定时交替出现的进位和借位脉冲调相作用相互抵消,输出时钟Fout 稳定。

3 改进的数宇锁相环结构及工作原理

3.1 改进的数字锁相环设计思路及其结构

如图2所示,在异或门鉴相器与K模可逆计数器之间插入一个Se的调节器对Se的波形进行调节,即给了K模计数器一个虚假的输出信号与输入信号的相位差Se_out。当伪相位差信号Se_out为方波时输出与输入信号锁定在一个特定的相位。

|

我们假定输出信号Fout与输入信号Fin正交时二者相差为零。设输出信号滞后于输入信号环路锁定相位羞为负,输出信号超前于输入信号环路锁定相位差为正。用Option信号选择锁定方式并输入相位差值。分别分析锁定相位差为负和锁定相位差为正环路进入锁定时各个信号之间的相位关系,很直观地得到Se调节器的实现方法。

3.2.1 锁定相位差为负Se调节器的设计实现

系统时钟Clk,输入信号Fin、输出信号Fout,相位差信号Se与伪相位差信号Se_out的相位关系如图3所示。伪相位差信号Se_out为一占空比为50%的方波,系统锁定。此时输出信号滞后于输入信号一定的相位,记为off-set。相位差信号Se高电平占空比低于伪相位差信号Se_out高电平占空比的值就是输出信号滞后于输人信号的相位offset。Se调节器要完成的工作就是将Se调整为Se_out的波形,即将Se为低电平宽度为offset的区域转换成高电平。具体实现为:设计一个预置值为offset的计数器。在Se为高电平时Se保持不变,同时计数器计数值保持为O,在Se由高电平变为低电平后开始加计数,当计数值未达到预置值offset。时Se仍保持为高电平,当计数值超过预置值offset时,将Se置低电平,这样得到的波形就是所需要的se_out。

|

系统时钟Clk、输入信号Fin,输出信号Fout,相位差信号Se与伪相位差信号Se_out的相位关系如图4所示。与输出信号滞后于输人信号环路锁定类似:设计一个预置值为offset的计数器。在Se为低电平时Se保持不变,同时计数器计数值保持为O,在Se由低电平变为高电平后开始加计数,当计数值未达到预置值offset时Se仍保持为低电平,当计数值超过预置值offset时,将Se置高电平,这样得到的波形就是所需要的Se_out。

|

电压 电路 仿真 FPGA 振荡器 Verilog Mentor Xilinx 示波器 相关文章:

- 选择最佳的电压基准源(11-29)

- 对电压参考进行滤波以获得低噪声性能(01-16)

- 可编程快速充电管理芯片MAX712/ MAX713及其应用(01-23)

- 改进型全桥移相ZVS-PWMDC/DC变换器(01-23)

- 负输出罗氏变换器实用性剖析(01-09)

- 通信电源设备对杂音电压的控制要求(02-13)