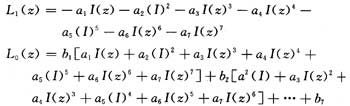

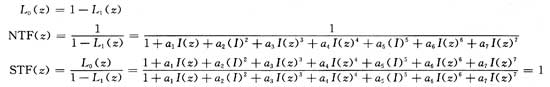

其中I(z)=1/(z-1),取b2=b3=b4=b5=b6=b7=0,b1=b8=1,则:

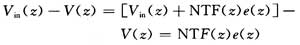

可以看到:a1,a2,a3,a4,a5,a6,a7决定NTF的极点,STF是1。而且,

这样,信号没有经过环路滤波器,只有量化噪声(e)经过环路滤波器,减少了信号通过环路滤波器时引起的失真,也减轻了具体环路滤波器电路的设计难度,而且环路滤波器的参数随温度和工艺偏差的改变不会影响信号。上面的推倒没有考虑c1,c2,…,c8和g1,g2,g3,见图3。为防止积分器输出饱和,实际c1,c2,…,c8和b1值都小于1,会在一定程度上减小信噪比。为NTF零点优化,g1,g2,g3实现内部负反馈,可以提高信噪比。

通过Simulink的仿真,可以合理确定这些参数。

本文设计的NTF零极点见图4。调制器的信噪比达到130 dB以上,最大稳定输入值达到0.9(被参考电压归一化),并且最后确定的所有参数值都很合理,便于集成电路的实现,调制器的仿真结果见图5(a),其仿真输入信号是频率700 Hz,幅值0.8的正弦波。

4 结果仿真和验证

图3给出整个D类功放的Simulink仿真模型,其中实际功率管的噪声用功率管噪声模型表示。噪声可分为2部分:一部分是随机噪身;一部分是输入信号的非线性失真。在仿真时采用高斯分布信号替代随机噪声,噪声底部是-65 dB;非线性失真用二次谐波表示(忽略更高次谐波),该谐波的幅直为-30 dB,把两部分噪声信号加起来的频谱参见图5(b)(实际功率管带来的噪声一般不会大于本文模型里用的噪声)。很显然,若功率管这部分噪声不做任何处理,就会严重影响音质。若采用类似文献[4]处理该噪声的方法,采用图3的新型调制器拓扑结构,就更加明显有效抑制了音频信号频带范围里的噪声,可以实现高保真的音质。图5(c)给出总体D类功放拓扑结构的仿真结果,其输入信号和仿真图5(a)一样,频率为700 Hz、幅值0.8的正弦波,并且用图3中的功率管模型噪声替代实际功率管噪声。通过比较图5(a),(b),(c),可以看到,虽然考虑实际功率管噪声而降低了信噪比5 dB,但∑-△调制器有效得调制了功率管带来的噪声,明显降低了D类功放的非线性失真,而且信噪比也大于文献[4]中结果。从而也验证了本文结构优点。

5 结语

本文介绍了基∑-△调制器带反馈的D类功放,尝试从新的角度研究高阶1-bit∑-△调制器的工作过程和设计思路,通过具体设计仿真,实现一个低非线性失真、信噪比可达到130 dB以上的7阶1-bit∑-△调制器。该调制器与目前出现的高阶∑-△调制器相比,有很多优点,用在基∑-△调制器带反馈的D类功放中,使功放达到高功率转化效率、高保真的要求。

|

|