D类功放中的∑-△调制器分析与设计

时间:11-27

来源:21IC

点击:

1 引 言

D类(数字音频功率)功率放大器由于功率转化效率高、散热量低的优点成为样的目前研究的热点,并且有望在几年内会取代目前主流的AB类功放成为音频功率放大器领域的主流产品。虽然D类功率放大器有很大的潜力,但还存在不同于传统功率放大器的缺点--非线性失真,这种非线性失真是阻止D类功放目前普遍应用的主要障碍之一。造成D类功率放大器非线性失真的原因很多,例如:通常设置死区时间来避免上下功率晶体管同时处于导通状态,由此会带来非线性失真;功放管的导通时间和体二极管恢复时间的有限造成的非线性失真;输出滤波电感与电容的非线性和电源的波动产生的非线性失真等。其中,功放管造成的非线性失真是D类功放噪声的主要部分。要设计一个高保真的D类功率放大器,就要尽力把这些非线性失真减到最小,这就需要采用一些新的技术手段来克服非线性失真的缺点。

为了减小非线性失真,与传统PwM控制的D类功放和没有带反馈的1-bit∑-△调制器控制的D类功放不同,出现了带反馈的1-bit∑-△调制器的D类功率放大器。本文在这种带反馈的1-bit∑-△调制器结构的基础上,设计一种低非线性失真拓扑的7阶1-bit∑-△调制器,并通过计算机仿真软件来仿真和验证的所设计的系统结构。

2 基于1-bit∑-△调制器的带反馈的D类功放系统结构

传统D类功率放大器的主要原理是一种将输入模拟音频信号或PCM数字信息变换成PWM(脉冲宽度调制)或PDM(脉冲密度调制)的脉冲信号,然后用PWM或PDM的脉冲信号去控制大功率开关器件通或断的音频功率放大器。虽然这种控制方法输入稳定范围大,但如引言所述,会产生大量的非线性失真,并且功放管输出端存在大量调制信号的谐波,这些谐波会产生有害的电磁辐射。

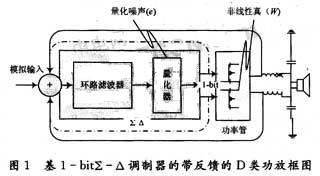

为了克服这些缺点,文献[3,4]在基于1-bit∑-△调制器的D类功放中做了改进,提出基于1-bit∑-△调制器的带反馈的D类功放,其系统结构见图1。如在图中量化器输出端反馈(见图中虚线)就构成一个∑-△调制器,其工作原理是利用过采样技术减少信号频带里的量化噪声,再用噪声整形技术把信号频带里的量化噪声推向高频,然后把高频部分滤掉,从而提高信噪比。如果不在量化器的输出端反馈(见图中虚线),而在功率管输出端反馈(见图中实线),则可以利用过采样和噪声整形这两种技术同时减少信号频带范围内量化器的量化噪声和功率管带来的非线性失真噪声,得到整体信噪比的提高。文献[3,4]就按照这种思路,设计出基于1-bit∑-△调制器的带反馈的D类功放,并得到实际流片的证实。值得提出的是根据输出信号幅度大小来设置量化器的迟滞,可以有效抑制功率管输出的高频成分,大量减少有害的电磁辐射。对于这种结构的D类功放,难点是设计一个高稳定输入、高信噪比的∑-△调制器来实现高功率转化效率和高保真音质。

3 新型7阶1-bit∑-△调制器结构与设计

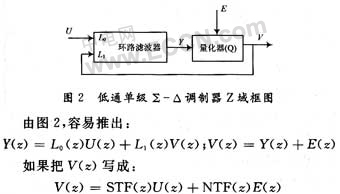

在模拟输入的D类功放中,只能选择单级1-bit∑-△调制器作为控制器,不能选择多位或级联结构。这里从新的角度阐释单级1-bit∑-△调制器的工作原理和设计思路。低通单级1-bit∑-△调制器可以分成2个部分:一部分是由L0和L1构成的线性环路滤波器,一部分是量化器,见图2。U是模拟信号输入;Y是环路滤波器的输出,也是量化器的输入;E是量化器的量化噪声;V是调制器的输出并负反馈到环路滤波器的输入。

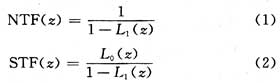

则调制器的噪声传输函数NTF(z)和信号传输函数STF(z)分别是:

由式(1)和(2)可知:在信号频率范围内,L1必须很大,才能使NTF很小,也就减小了信号频率范围内的量化噪声;同时在信号频率范围内,L0必须很大,这样可以抵消必须很大的L1,以迫使NTF保持不变,让信号不失真地通过;并且NTF和STF有相同的极点。进一步推知:L1和L0应该有相同的极点。但是他们的零点一般不同。其实,一般用积分器电路来实现L1和L0,的确实现了有相同极点的L1和L0。如一阶∑-△调制器:L0=1/(z+1);L1=-1/(z+1),可得到STF=z-1,NTF=z-1-1,从而实现了一阶噪声整形。环路滤波器中级联积分器个数代表调制器的阶数(n),通过L1可以得到NTF。阶数越高,就可以得到更高阶的噪声整形,就越能降低信号频率范围内的量化噪声,实现更高的信噪比。1-bit调制器的阶数、过采样率和信噪比的具体数学关系在文献[6,7]里有详细的推导。

∑-△调制器的信噪比取决于NTF,所以设计调制器时,首先根据系统要求,选择合适的过采样率和阶数,构造L1,再由式(1)得到NTF。为使信噪比最大,对NTF极点的位置要求很苛刻,其位置要使得NTF分母的模在信号频率范围内很大(为降低信号频率范围的量化噪声),并且尽可能保持不变(为不影响信号频率范围里的信号)。但是,对于单级高阶∑-△调制器,设计这样的NTF使信噪比最大的同时,也使得最大稳定输入值减小。NTF的零点一般都位于z=1,但是NTF零点全部都在z=1时,没有让调制器的信噪比达到最大。在过采样率和阶数都确定的条件下,特别对于单级高阶∑-△调制器的设计,需要优化NTF的零点,让调制器的信噪比进一步得到提高,即在电路内部引进负反馈,让NTF的部分零点偏离1。确定了NTF,接下来设计STF,为简化设计,一般让STF在信号频率范围内接近1,实现输入信号的无失真传输。通过上述分析看到:设计∑-△调制器,也就是设计设计L0和L1使得NTF和STF满足系统对信噪比的要求。

∑-△调制器应用在D类功放中,因为输出功率管的电磁辐射和功率管寄生电容消耗的能量随过采样频率的增大而增大,所以不能取很高的过采样频率。本文取过采样值128,对频率范围20 Hz~21 kHz的音频信号,即过采样频率是5.6 MHz。

高保真音频功率放大器都要求信噪比达到100 dB以上。在采样频率确定的条件下,要实现100 dB以上的信噪比,又必须使用单级1-bit的∑-△调制器,就要选择高阶调制器。采样率为128的4阶的调制器,如前面所述,如果严格要求NTF的极点位于对信噪比的影响最小的位置,可以很容易实现100 dB以上的信噪比,但是按这种的思路设计,若输入值超过0.7(归一化),调制器就变的不稳定。用在D类功放中,最大功率转化效率是70%,显然这样的设计不可取,没有充分体现D类功放的高功率转化效率的优点。

但是在NTF和阶数之间做折衷,对NTF极点位置的要求不像前面所述的那样苛刻,最大稳定输入值就会变大。虽然这样的NTF降低了信噪比,但是采用高阶,比如6阶或7阶,来提高信噪比,最后整体信噪比也能达到100 dB以上,最大稳定输入值得到很大程度的提高。本文采用这种思路,经过仿真,采用过采样率为128的7阶调制器。其拓扑结构见图3,其中第2、第4、第6积分器是采用没有延迟的积分器,其余的积分器采用一个周期延迟的积分器,目的为优化NTF零点便于实际电路的实现。与目前出现的高阶调制器结构相比,这种结构有很多优点,更适用于基于1-bit∑-△调制器的带反馈的D类功放。为了简化分析,先假设c1=c2=…=c8=1,g1=g2=g3=0,可以推出:

D类(数字音频功率)功率放大器由于功率转化效率高、散热量低的优点成为样的目前研究的热点,并且有望在几年内会取代目前主流的AB类功放成为音频功率放大器领域的主流产品。虽然D类功率放大器有很大的潜力,但还存在不同于传统功率放大器的缺点--非线性失真,这种非线性失真是阻止D类功放目前普遍应用的主要障碍之一。造成D类功率放大器非线性失真的原因很多,例如:通常设置死区时间来避免上下功率晶体管同时处于导通状态,由此会带来非线性失真;功放管的导通时间和体二极管恢复时间的有限造成的非线性失真;输出滤波电感与电容的非线性和电源的波动产生的非线性失真等。其中,功放管造成的非线性失真是D类功放噪声的主要部分。要设计一个高保真的D类功率放大器,就要尽力把这些非线性失真减到最小,这就需要采用一些新的技术手段来克服非线性失真的缺点。

为了减小非线性失真,与传统PwM控制的D类功放和没有带反馈的1-bit∑-△调制器控制的D类功放不同,出现了带反馈的1-bit∑-△调制器的D类功率放大器。本文在这种带反馈的1-bit∑-△调制器结构的基础上,设计一种低非线性失真拓扑的7阶1-bit∑-△调制器,并通过计算机仿真软件来仿真和验证的所设计的系统结构。

2 基于1-bit∑-△调制器的带反馈的D类功放系统结构

传统D类功率放大器的主要原理是一种将输入模拟音频信号或PCM数字信息变换成PWM(脉冲宽度调制)或PDM(脉冲密度调制)的脉冲信号,然后用PWM或PDM的脉冲信号去控制大功率开关器件通或断的音频功率放大器。虽然这种控制方法输入稳定范围大,但如引言所述,会产生大量的非线性失真,并且功放管输出端存在大量调制信号的谐波,这些谐波会产生有害的电磁辐射。

为了克服这些缺点,文献[3,4]在基于1-bit∑-△调制器的D类功放中做了改进,提出基于1-bit∑-△调制器的带反馈的D类功放,其系统结构见图1。如在图中量化器输出端反馈(见图中虚线)就构成一个∑-△调制器,其工作原理是利用过采样技术减少信号频带里的量化噪声,再用噪声整形技术把信号频带里的量化噪声推向高频,然后把高频部分滤掉,从而提高信噪比。如果不在量化器的输出端反馈(见图中虚线),而在功率管输出端反馈(见图中实线),则可以利用过采样和噪声整形这两种技术同时减少信号频带范围内量化器的量化噪声和功率管带来的非线性失真噪声,得到整体信噪比的提高。文献[3,4]就按照这种思路,设计出基于1-bit∑-△调制器的带反馈的D类功放,并得到实际流片的证实。值得提出的是根据输出信号幅度大小来设置量化器的迟滞,可以有效抑制功率管输出的高频成分,大量减少有害的电磁辐射。对于这种结构的D类功放,难点是设计一个高稳定输入、高信噪比的∑-△调制器来实现高功率转化效率和高保真音质。

3 新型7阶1-bit∑-△调制器结构与设计

在模拟输入的D类功放中,只能选择单级1-bit∑-△调制器作为控制器,不能选择多位或级联结构。这里从新的角度阐释单级1-bit∑-△调制器的工作原理和设计思路。低通单级1-bit∑-△调制器可以分成2个部分:一部分是由L0和L1构成的线性环路滤波器,一部分是量化器,见图2。U是模拟信号输入;Y是环路滤波器的输出,也是量化器的输入;E是量化器的量化噪声;V是调制器的输出并负反馈到环路滤波器的输入。

则调制器的噪声传输函数NTF(z)和信号传输函数STF(z)分别是:

由式(1)和(2)可知:在信号频率范围内,L1必须很大,才能使NTF很小,也就减小了信号频率范围内的量化噪声;同时在信号频率范围内,L0必须很大,这样可以抵消必须很大的L1,以迫使NTF保持不变,让信号不失真地通过;并且NTF和STF有相同的极点。进一步推知:L1和L0应该有相同的极点。但是他们的零点一般不同。其实,一般用积分器电路来实现L1和L0,的确实现了有相同极点的L1和L0。如一阶∑-△调制器:L0=1/(z+1);L1=-1/(z+1),可得到STF=z-1,NTF=z-1-1,从而实现了一阶噪声整形。环路滤波器中级联积分器个数代表调制器的阶数(n),通过L1可以得到NTF。阶数越高,就可以得到更高阶的噪声整形,就越能降低信号频率范围内的量化噪声,实现更高的信噪比。1-bit调制器的阶数、过采样率和信噪比的具体数学关系在文献[6,7]里有详细的推导。

∑-△调制器的信噪比取决于NTF,所以设计调制器时,首先根据系统要求,选择合适的过采样率和阶数,构造L1,再由式(1)得到NTF。为使信噪比最大,对NTF极点的位置要求很苛刻,其位置要使得NTF分母的模在信号频率范围内很大(为降低信号频率范围的量化噪声),并且尽可能保持不变(为不影响信号频率范围里的信号)。但是,对于单级高阶∑-△调制器,设计这样的NTF使信噪比最大的同时,也使得最大稳定输入值减小。NTF的零点一般都位于z=1,但是NTF零点全部都在z=1时,没有让调制器的信噪比达到最大。在过采样率和阶数都确定的条件下,特别对于单级高阶∑-△调制器的设计,需要优化NTF的零点,让调制器的信噪比进一步得到提高,即在电路内部引进负反馈,让NTF的部分零点偏离1。确定了NTF,接下来设计STF,为简化设计,一般让STF在信号频率范围内接近1,实现输入信号的无失真传输。通过上述分析看到:设计∑-△调制器,也就是设计设计L0和L1使得NTF和STF满足系统对信噪比的要求。

∑-△调制器应用在D类功放中,因为输出功率管的电磁辐射和功率管寄生电容消耗的能量随过采样频率的增大而增大,所以不能取很高的过采样频率。本文取过采样值128,对频率范围20 Hz~21 kHz的音频信号,即过采样频率是5.6 MHz。

高保真音频功率放大器都要求信噪比达到100 dB以上。在采样频率确定的条件下,要实现100 dB以上的信噪比,又必须使用单级1-bit的∑-△调制器,就要选择高阶调制器。采样率为128的4阶的调制器,如前面所述,如果严格要求NTF的极点位于对信噪比的影响最小的位置,可以很容易实现100 dB以上的信噪比,但是按这种的思路设计,若输入值超过0.7(归一化),调制器就变的不稳定。用在D类功放中,最大功率转化效率是70%,显然这样的设计不可取,没有充分体现D类功放的高功率转化效率的优点。

但是在NTF和阶数之间做折衷,对NTF极点位置的要求不像前面所述的那样苛刻,最大稳定输入值就会变大。虽然这样的NTF降低了信噪比,但是采用高阶,比如6阶或7阶,来提高信噪比,最后整体信噪比也能达到100 dB以上,最大稳定输入值得到很大程度的提高。本文采用这种思路,经过仿真,采用过采样率为128的7阶调制器。其拓扑结构见图3,其中第2、第4、第6积分器是采用没有延迟的积分器,其余的积分器采用一个周期延迟的积分器,目的为优化NTF零点便于实际电路的实现。与目前出现的高阶调制器结构相比,这种结构有很多优点,更适用于基于1-bit∑-△调制器的带反馈的D类功放。为了简化分析,先假设c1=c2=…=c8=1,g1=g2=g3=0,可以推出:

- 音频系统应用中的“POP”噪声以其常用解决方法(12-01)

- 20位单片音频数模转换器PCM63P (01-22)

- TDA2030音频功率放大电路(02-07)

- 适合音频扩展基座设计的完整音频解决方案(06-03)

- 基于DPPC2006的数字音频功率放大器(05-05)

- 新型人机对话接口与音频数据转换器技术及选用(05-23)