如何用C语言描述AES256加密算法最高效?

和列混合变换 (MixColumns) 步骤流水线化,以提高性能。在这些函数中,我们通过将编译指示放在第一个循环中来执行 HLS Pipeline 命令。我们应展开内部循环。这些函数中有几个函数从查找表(通常从 block RAM 构建)读取数据。我们需要增加存储器带宽,在本例中,我将编译指示参数指定为"完成",这样可将存储器内容实现为分立寄存器而非BRAM。

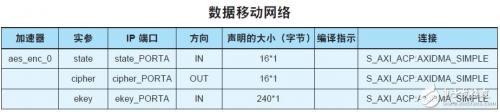

在 Zynq SoC 上的 PS 与 PL 之间传输数据的能力对提升性能而言也非常重要。我所做的第一步是将数据移动时钟网络设定为最高时钟频率:200MHz。第二个方案是确保为 PS 与 PL 之间的数据传输使用直接存储器访问。为此,我必须将接口稍加修改,并使用 sds_alloc 函数按照 DMA 传输的要求确保数据在存储器中的连续性(图 7)。

图 7 - PS 与 PL 之间的数据移动网络

第二个也是最后的优化步骤是将硬件功能的时钟速率设定在所支持的最高频率:166.67 MHz。

操作系统支持

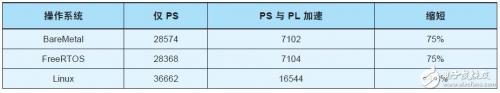

当我最终将所有内容放在一起并构建出这个实例时,经 PL 加速的 AES 代码在 Linux 上运行16,544 个处理器时钟周期; 当在单独在软件中运行

AES 代码时,只需要 45%(16,544/36,662) 的周期数量。这可将这个具有互相依赖关系且相当复杂的算法的执行时间缩短 55%。

当然,我们也可在 SDSoC 环境中选择 BareMetal或 FreeRTOS 操作系统。创建 BareMetal 和 FreeRTOS项目并重新使用代码能够在三种操作系统之间进行性能对比。对于给定项目而言,操作系统的选择取决于任务要求、性能预算以及响应时间。

图 8 给出了 Zynq SoC 的 PS 和 PL 中三种操作系统的性能( 图 8)。

图 8 - Zynq PS 和 PL 中的操作系统性能。FreeRTOS 和 BareMetal 提供类似的缩短效果。

不出意料,FreeRTOS 和 BareMetal 实现了类似的时间缩短效果,因为两种操作系统都比完整的 LinuxOS 简单得多。

正如我们的结果所示,利用 SDSoC 开发环境加速 AES 加密,能实现真正的性能提升,而且易于实现-- 无需深入的 FPGA 设计经验。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)