大容量存储的NOR FLASH的原理及应用

VDRF256M16是珠海欧比特公司自主研发的一种高速、大容量的NOR FLASH,可利用其对大容量数据进行高速缓存。文中介绍了该芯片的结构和原理,并同时给出了一个系统中大容量、高速数据传输要求的设计方案。

1引言

NOR FLASH 是很常见的一种存储芯片,数据掉电不会丢失。NOR FLASH 支持Execute On Chip,即程序可以直接在FLASH 片内执行。这点和NAND FLASH 不一样。因此,在嵌入是系统中,NOR FLAS H 很适合作为启动程序的存储介质。NOR FLAS H 的读取和RAM很类似,但不可以直接进行写操作。对NOR FLAS H 的写操作需要遵循特定的命令序列,最终由芯片内部的控制单元完成写操作。所以,NOR FLASH一般是作为用于程序的存储与运行的工具。

NOR的特点是芯片内执行(XIP, Execute In Place),这样应用程序可以直接在FLASH闪存内运行,不必再把代码读到系统RAM中。NOR FLASH的传输效率很高,在1~4MB的小容量时具有很高的成本效益,但是很低的写入和擦除速度大大影响了它的性能。

2NAND FLASH与NOR FLASH的性能比较

FLASH闪存是非易失存储器,可以对称为块的存储器单元块进行擦写和再编程。任何FLASH器件的写入操作只能在空或已擦除的单元内进行,所以大多数情况下,在进行写入操作之前必须先执行擦除。NAND FLASH器件执行擦除操作是十分简单的,而NOR FLASH则要求在进行擦除前先要将目标块内所有的位都写为0。

由于擦除NOR FLASH器件时是以64~128KB的块进行的,执行一个写入/擦除操作的时间为5s,与此相反,擦除NAND FLASH器件是以8~32KB的块进行的,执行相同的操作最多只需要4ms。

执行擦除时块尺寸的不同进一步拉大了NOR FLASH和NADN FLASH之间的性能差距,统计表明,对于给定的一套写入操作(尤其是更新小文件时更多的擦除操作必须在基于NOR FLASH的单元中进行。

NAND FLASH的单元尺寸几乎是NOR FLASH器件的一半,由于生产过程更为简单,NAND FLASH结构可以在给定的模具尺寸内提供更高的容量,也就相应地降低了价格。

NOR FLASH占据了容量为1~16MB闪存市场的大部分,而NAND FLASH只是用在8~128MB的产品当中,这也说明NOR主要应用在代码存储介质中,NAND FLASH适合于数据存储,NAND FLASH在Compact Flash、Secure Digital、PC Cards和MMC存储卡市场上所占份额最大

3VDRF256M16芯片

3.1芯片介绍

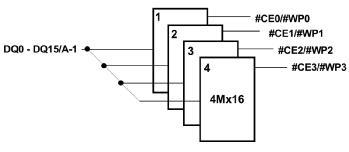

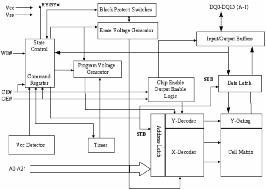

VDRF256M16是一款高集成度的静态随机存取存储器,其总含有256M bits。由于此芯片里面包含4个片选,每个片选含有1个Block,具体的内部结构见图1。这种结构不但大大的扩充了存储器的容量和数据位宽,而且还可以在应用时大量节省了PCB板的使用空间。从图1可以看出,每个片选控制了每一Block的写保护信号#WP,另外芯片中的每一个Block的其他控制端口、地址线和数据线都是共用的。图2为VDRF256M16中的任一Block的结构框图,它主要由控制逻辑、存储整列等组成。下面为VD RF256M16的主要特性。

-总容量:256Mbit;

-数据宽度:16位;

-工作电压3.3V +/- 0.3V;

-每个DIE(共4个DIE)含:-8个8KB的扇区、127个64KB的扇区;

-扇区的硬件锁防止被擦除、编程;

-存取时间最高达90ns;

-高擦除/编程速度:

-字编程8us(典型值);

-扇区擦除500ms(典型值);

-芯片擦除64s/DIE(典型值);

-解锁旁路模式;

-擦除暂停/继续模式;

-支持JEDEC通用FLASH接口协议(CFI);

-写保护功能,允许不管扇区保护状态对两BOOT扇区进行写保护;

-加速功能促进加快芯片编程时间;

-最小100000次的擦除、编程;

图1 VDRF256M16芯片内部的结构图

图2 VDRF256M16内部Block的结构框图

3.2VDRF256M16的引脚说明

VDRF256M16芯片采用的是SOP封装工艺,整块芯片表面镀金,这样可以大幅度增强了芯片的抗干扰和抗辐射的能力,有利于该芯片能应用于航空航天等恶劣的环境。

VDRF256M16芯片各引脚分布见下图3所示,各引脚的功能说明如下:

VCC:+3.3V电源输入端。滤波的旁路电容应尽可能靠近电源引脚, 并直接连接到地;

VSS:接地引脚;

A[21..0]:地址同步输入端;

#WE:此端为低时写入,为高时写无效,数据有效发生在相应地址有效之后的两个周期;

# OE:输出使能, 数据读取时需置为低,写时置为低;

#WP/ACC[3..0]:最外的两个8KB的BOOT扇区保护状态。当电平为VIL时,此两扇区受保护,不能进行擦除、编程操作;当电平为VIH时,取决于扇区保护状态,如此两扇区是受保护的则不能进行操作,如未受保护则可进行擦除、编程操作;当电平为VHH时,将进入解锁旁路模式进入加速编程状态。此管脚不能悬

- 可管理NAND:适用于移动设备的嵌入式大容量存储(01-14)

- 基于车载CAN总线记录仪的大容量存储系统设计方案(12-21)

- CC-Link的优势有哪些(12-16)

- stm32小容量、中容量和大容量产 在选择启动文件时该怎么选(11-17)

- stm32 大容量芯片烧录出错(11-13)

- HOLTEK推出HT24LC128新款大容量串行式EEPROM(09-12)