大容量存储的NOR FLASH的原理及应用

空;

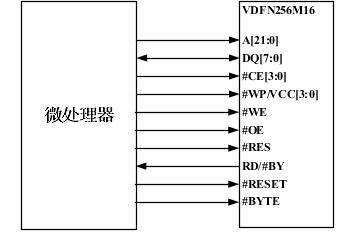

#CE[3..0]:低电平有效时选中该片,可通过两个片选信号选择四个Block,但两个片选信号不能同时选中;

#BYTE:字节/字模式选择。低电平为字节模式,DQ0~DQ7为数据端口,DQ8~DQ14为高阻状态,DQ15做LSB地址输入;高电平为字模式,DQ0~DQ15为数据端口;

RY/#BY:准备/忙碌状态输出。低电平为忙碌状态;高电平为准备状态;

D[15..0]:数据输入/输出脚。

图3 VDRF256M16引脚分布图

3.3芯片操作

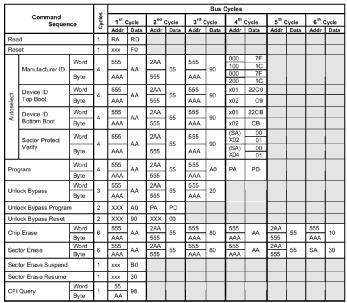

VDRF256M16的软件操作可以分成两类: 普通读操作和命令操作。普通读操作非常简单, 与RAM的读操作类似, 当#OE和#CE信号同时为低电平时, 即可从芯片读出数据。芯片的命令操作包括芯片的识别、字节编程、扇区擦除以及整片擦除等。这些操作分别由各自的软件操作命令序列来完成, 如表1所列。其中, BA为待编程字节的地址,Data为字节编程数据, SAX为待擦除扇区的地址。命令中的地址只有低15位有效, 高4位可任意设置为/ 00或/ 10。VDRF256M16的软件操作命令序列实际上是由一个或多个总线写操作组成的。以VDRF256M16的扇区擦除为例, 其操作过程包括3个步骤: 第1步, 开启擦除方式,用表1中给出的第1至第5周期的总线写操作来实现; 第2步, 装载扇区擦除命令( 30H) 和待擦除扇区的地址, 用其对应的第6周期的总线写操作来实现; 第3步, 进行内部擦除。内部擦除时间最长为500ms。

表1 软件操作命令序列表

总线写操作时,OE必须保持为高电平, CE和WE应为低电平。地址和数据的锁存由CE和WE两个信号的边沿进行控制。它们当中后出现的下降沿将锁存地址, 先出现的上升沿将锁存数据。

4VDRF256M16芯片的应用

以VDRF256M16为核心,配合适当的控制信号,不但可以对存储器进行各种读写操作,而且还可以进行进一步的容量拓展。下面以该芯片在系统中的应用为例,介绍VDRF256M16在系统中的的硬件设计及各信号之间的时序关系。

4.1系统的工作原理

硬件设计就是搭建合适的接口电路, 将VDRF256M16连接到微处理器的系统总线上。根据VDRF256M16和微处理器的结构特性, 我们发现VDRF256M16的数据线、读、写等信号线可以很容易地连接到微处理器的系统总线上。

图4 硬件电路原理图

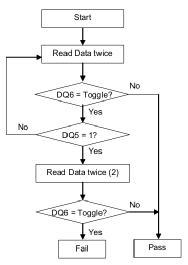

微处理器接到指令,需将数据或程序存放至NOR FLASH时,微处理器首先会发送擦除指令将芯片进行擦除,具体的流程见图5。然后将数据或程序利用写指令写到FLASH中。当需要调取数据或程序指令的时候,需要从FLASH中调取程序,那就需要发送读指令到FLASH中,具体的流程见图6。

图5 擦除指令流程图

图6 读指令流程

4.2控制时序

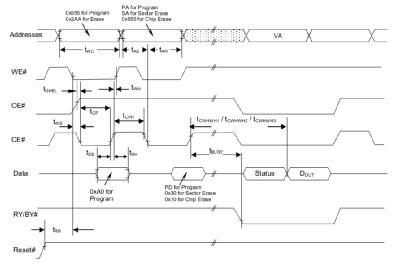

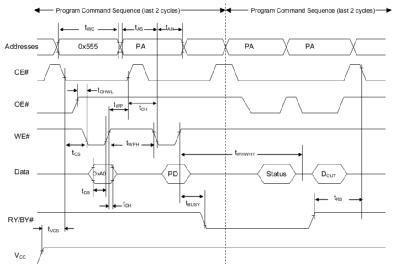

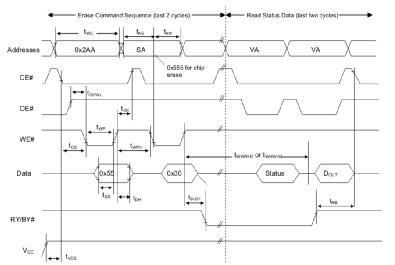

由于该设计的数据速度快,容量大,因此时序的配合很重要,这种配合不仅仅指单个Block中各信号与时钟的配合,同时也应考虑Block与Block之间的各信号之间的配合。当数据输入时地址和数据应在保持稳定;而数据输出时,地址也应保持稳定,这样才能保证数据传输的可靠性及连续性。图5(读时序)和图6(写时序)为单片Block的控制时序图。从图中可以看出:无论在读或写数据时,地址总线信号和控制信号在发送一段时间后,数据信号才能发送或者读取。所以在使用时,必须注意时序上的延时。

图7 单片Block的写时序图

图8 单片Block的读时序图

图8 单片Block的擦除时序图

5结束语

本文所介绍的VDRF256M16是一款高速度、存储容量大的16位NOR FLASH存储器,总容量达到了256M,存储周期最大可达到90ns。16位的数据总线宽度能更好和更快速的采集和缓存数据。在实际的应用中,可作为高速缓存。但在使用的过程中需要注意写入和读取数据的延时问题。另外,本芯片能在相当大的应用范围中使用,具有很好的通用性,在需要高速大容量数据存储的场合的工程中比其他类型的存储器更有应用价值。

- 可管理NAND:适用于移动设备的嵌入式大容量存储(01-14)

- 基于车载CAN总线记录仪的大容量存储系统设计方案(12-21)

- CC-Link的优势有哪些(12-16)

- stm32小容量、中容量和大容量产 在选择启动文件时该怎么选(11-17)

- stm32 大容量芯片烧录出错(11-13)

- HOLTEK推出HT24LC128新款大容量串行式EEPROM(09-12)