HyperLink编程和性能考量

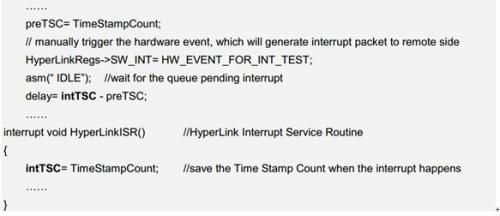

一个DSP可以通过HyperLink来触发另外一个DSP的中断。通过HyperLink传递中断的延迟通过下列的伪代码获得测量。

测试是在Loopback模式下测试。

1GHz C6670的测试结果是大概710个DSP core cycles.

4、范例工程

本文的范例代码在C6670EVM上通过测试。EVM板子上有两个C6670 DSP,他们通过HyperLink互联。

在这个例子中,DSP1存储空间通过HyperLink被映射到了DSP0上。DSP0通过HyperLink窗口访问DSP1的存储空间就像访问自己的本地空间一样。这个工程范例也支持loopback模式。在loopback模式下,DSP0事实上是通过自己的HyperLink窗口访问了自己的本地地址空间。

本例也演示了通过HyperLink来实现中断传递。

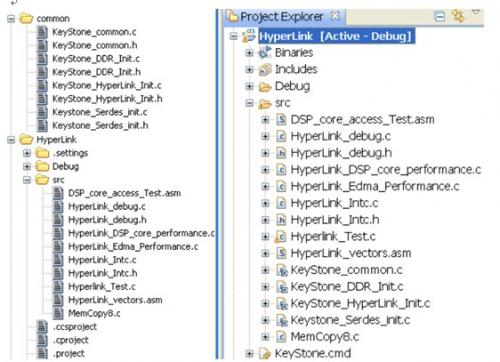

工程代码的目录结构如下图所示。

图7工程代码目录树

该示例代码同样可以在其他KeyStone DSP EVM板上运行。只是如果板子上只有一个DSP芯片,那么只能运行loopback模式。

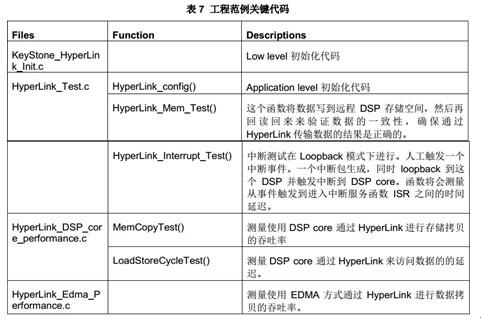

下表列出了KeyStone工程的关键代码列表。

运行这个范例工程的步骤:

1.连通CCS与DSP EVM.

2.下载代码到core 0 of DSP0.

3.下载代码到core 0 of DSP1.

4.先运行DSP1 ,然后运行DSP0. (如果EVM上只有一个DSP,且运行在loopback模式下,那么直接下载到DSP0,再运行)

5.检测每个DSP的stdout窗口,验证测试结果。

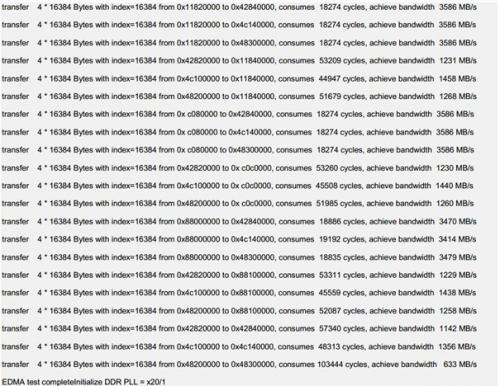

典型的输出信息如下:

用户可以在HyperLink_Test.c中的HyperLink_config()函数中修改初始化值,然后重新编译来验证在不同配置下的HyperLink性能。

这个例子是在CCS5.1下编译,使用pdk_c6618_1_0_0_5.如果在你的电脑上进行重新编译新的配置,你可能需要修改csl包含路径。

参考资料

1. KeyStone Architecture HyperLink User Guide (SPRUGW8)

2. TMS320C6670 datasheet (SPRS689)

HyperLink KeyStone 远程访问 中断延迟 相关文章:

- 基于KeyStone 器件建立鲁棒性系统(10-29)

- 在KeyStone 器件实现IEEE1588 时钟方案(10-15)

- 基于多核处理器的弹载嵌入式系统设计研究(02-18)

- Navigator Runtime 最大限度提高多内核效率(05-08)

- 基于KeyStone DSP的多核视频处理技术(09-15)

- KeyStone多核SoC工具套件: 单个平台满足所有需求(09-07)